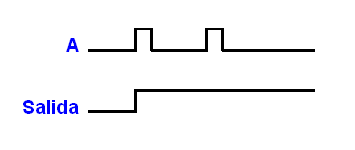

PROBLEMA: Analizar el siguiente circuito. Supóngase que la entrada A y la salida son inicialmente cero. Sugiérase también una forma de "limpiar el registro" (regresar la salida a su valor original de "cero")

Cuando la entrada A y la salida son inicialmente “cero” (“0”), el bloque OR está alimentado con dos ceros, produciendo la salida de cero.

Cuando activamos la entrada con un valor de A=1, el bloque OR producirá una salida de “1”, lo cual pondrá una entrada de “1” en el mismo bloque OR compatible con la salida de “1”.

Al volver a tomar la entrada A su valor de cero, el “1” a la entrada del OR producido por su salida mantendrá la salida del OR en el estado “1”. Esto es, cuando A toma el valor de “1”, la salida toma también el valor de “1” y permanece en ese estado por tiempo indefinido aún cuando A regrese a su valor original de “0”.

Este ejemplo demuestra una característica interesante e importante que juega la retroalimentación (feedback) en los circuitos lógicos. La retroalimentación proporciona memoria a los circuitos lógicos.

Un diagrama de tiempos característico del comportamiento del circuito sería como el siguiente:

Una forma de “limpiar el registro” (esto es, borrar la memoria) es añadiendo unos componentes de la siguiente manera:

Cuando no hay ninguna señal en R (o sea, cuando la entrada en la terminal R es R=0), por la acción del NOT inversor el bloque AND conectará directamente la salida del bloque OR a la entrada del mismo y no tendrá efecto alguno en el diagrama de tiempos del circuito previo. Este circuito se comportará exactamente como el circuito anterior.

Sin embargo, cuando se aplica una entrada de “1” a R, la compuerta AND interrumpirá la alimentación de la salida del OR a la entrada del mismo, “borrando” la memoria si es que la salida era “1” y la terminal S tenía el valor de “0”. En el caso de que R permanezca activada con un “1”, la salida tomará directamente el valor de S.

Obsérvese que arriba se llevó a cabo un ligero cambio en la notación de las terminales de entrada del circuito. A la entrada que lo puede “ajustar” con una salida de “1” se le ha designado con la letra S, una abreviatura de la palabra inglesa Set que significa precisamente “ajuste”, mientras que a la terminal con la cual se puede “reajustar” el circuito “limpiando” el registro previo se le ha designado con la letra R, una abreviatura de la palabra inglesa Reset que significa precisamente “reajuste”. Esto se ha hecho para ir adecuando nuestra notación con la notación utilizada en la mayoría de la literatura técnica.

Un diagrama de tiempos ilustrando todas las situaciones posibles se muestra a continuación:

La función de “limpieza de registro”es indispensable en una configuración de circuitos lógicos para borrar información previa y poder procesar información nueva.

PROBLEMA: El Flip-Flop R-S. Analizar el siguiente circuito considerando todas las 16 combinaciones posibles de unos y ceros (cuatro a la entrada y cuatro a la salida) descartando aquellos estados que resulten incompatibles. Asimismo, construír una Tabla de Verdad lo más simplificada posible para dicho circuito.

El análisis se llevará a cabo haciendo un diagrama independiente para cada una de las combinaciones posibles, trazando el flujo de los valores binarios y observando la compatibilidad de los mismos para cada combinación de valores. Empezaremos con la primera combinación en la cual supondremos que tanto las dos entradas R y S como las dos salidas Q y Q tienen valores de cero (puesto que una forma alterna muy común de simbolizar al inverso lógico de Q además de ponerle una barra horizontal encima a la Q consiste en agregarle una comilla sencilla posterior a Q, se estará usando esta simbolización alterna para ir acostumbrando al lector a ambas simbolizaciones):

R=0, S=0, Q=0, Q’=0:

El 0 que suponemos a la salida del NAND superior alimenta con dicho 0 una de las entradas del NAND inferior, el cual junto con el 0 que está siendo puesto en la terminal S producirá un 1 a la salida Q del NAND inferior. Este 1 es incompatible con el valor de 0 que estamos asumiendo para Q. Por otro lado, el 0 que suponemos a la salida del NAND inferior alimenta con dicho 0 una de las entradas del NAND superior, el cual junto con el 0 que está siendo puesto en la terminal R producirá un 1 a la salida Q del NAND superior. Este 1 es incompatible con el valor de 0 que estamos asumiendo para Q. Por lo tanto, se descarta por completo esta combinación de valores por no ser una combinación válida.

R=0, S=0, Q=0, Q’=1:

En este caso, de nueva cuenta el 0 que suponemos a la salida del NAND superior alimenta con dicho 0 una de las entradas del NAND inferior, el cual junto con el 0 que está siendo puesto en la terminal S producirá un 1 a la salida Q' del NAND inferior. Este 1 sí es incompatible con el valor de 1 que estamos asumiendo para Q'. Sin embargo, por otro lado, el 1 que suponemos a la salida del NAND inferior que alimenta con dicho 1 una de las entradas del NAND superior, junto con el 0 que está siendo puesto en la terminal R producirá un 1 a la salida Q del NAND superior. Este 1 es incompatible con el valor de 0 que estamos asumiendo para Q. Por lo tanto, también se descarta esta combinación de valores por no ser una combinación válida.

R=0, S=0, Q=1, Q’=0:

Podemos ver que este caso es similar al caso anterior, lo cual era anticipable por la simetría de la figura.

R=0, S=0, Q=1, Q’=1:

Al seguir el flujo de todas las señales con los valores supuestos, encontramos que en este caso los valores sí son compatibles. Por lo tanto, podemos hacer la siguiente Tabla de Verdad para los mismos:

R=1, S=0, Q=0, Q’=0:

Nuevamente, encontramos otra situación en la que la combinación de valores no es compatible, razón por la cual se descarta esta posibilidad.

R=1, S=0, Q=1, Q’=0:

Esta combinación de valores también se descarta por no ser una combinación compatible.

R=1, S=0, Q=0, Q’=1:

Los valores en este caso sí son compatibles, y por lo tanto podemos hacer una Tabla de Verdad para los mismos:

R=1, S=0, Q=1, Q’=1:

Esta es una combinación de valores que no es compatible, y por lo tanto se descarta.

R=1, S=0:

Antes de proseguir, para ahorrarnos trabajo podemos explotar a nuestro favor una simetría. Puesto que el circuito es simétrico en el sentido de que si tomamos lo volteamos por completo de arriba abajo tendremos en esencia lo mismo, al tratar los cuatro casos correspondientes a los valores de entrada R=0 y S=1 también estamos cubriendo los cuatro casos correspondientes a los valores de entrada R=1 y S=0 con la simple inversión de los elementos de arriba hacia abajo. En base a la simetría y los resultados obtenidos previamente, podemos afirmar que el único conjunto de valores compatibles para R=0 y S=1 es Q=1 y Q’=0, lo cual podemos resumir en la siguiente Tabla de Verdad:

Podemos proseguir con las combinaciones de valores faltantes:

R=1, S=1, Q=0, Q’=0:

Esta combinación de valores se descarta por ser totalmente incompatible.

R=1, S=1, Q=0, Q’=1:

En este caso la combinación de valores sí es compatible, y su Tabla de Verdad es:

R=1, S=1, Q=1, Q’=0:

Los valores en este caso también son compatibles, y su correspondiente Tabla de Verdad será:

Falta ya tan sólo una combinación posible de valores por checar. Es la siguiente:

R=1, S=1, Q=1, Q’=1:

Así, la última combinación posible de valores que nos faltaba por checar resulta ser totalmente incompatible, razón por la cual también se descarta.

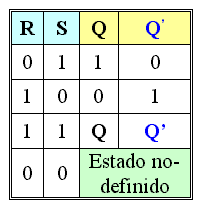

Podemos juntar ahora todas las Tablas de Verdad para este circuito en una sola:

Para simplificar esta Tabla de Verdad, como primera observación se nota que el único caso en el cual los valores de Q y Q' no son complementarios es R=0 y S=0. En la terminología técnica empleada en el estudio de los circuitos lógicos, este es un estado es conocido como un estado no-definido. Con esto en mente, y agrupando las salidas similares por razones que pronto quedarán claras, la Tabla de Verdad toma el siguiente aspecto:

Analizando esta Tabla de Verdad, encontramos algunos detalles interesantes. Si las entradas toman los valores R=1 y S=0, las salidas tomarán los valores Q=0 y Q’=1. Y si las entradas cambian a los valores R=0 y S=1, las salidas cambiarán a los valores Q=1 y Q’=0. Esto es, cuando las entradas son complementarias, Q toma el valor de S.

Al tomar las entradas los valores R=1 y S=1; existen dos salidas complementarias válidas. Esto indica que al tomar ambas R y S el valor de 1, se retendrán a la salida los valores de la condición previa, esto es, el circuito "recordará" su estado anterior. Por ejemplo, si la entrada tiene los valores R=1 y S=0, la salida tomará los valores Q=0 y Q’=1. Al tomar la entrada los valores R=1 y S=1, la salida seguirá reteniendo los mismos valores Q=0 y Q’=1. La única manera de invertir la salida Q es aplicando la condición R=0 y S=1. Después de aplicar dicha condición, el circuito mantendrá la salida de Q=1 y Q’=0 al aplicársele la condición R=1 y S=1.

Puesto que en el estado R=1 y S=1 las salidas pueden tomar dos valores que siempre serán complementarios, podemos simplificar aún más la Tabla de Verdad:

Esta Tabla nos quiere decir que para la condición R=1 y S=1, si Q toma el valor de 1 entonces Q’ tomará el valor de 0 o bien, si Q toma el valor de 0 entonces Q’ tomará el valor 1.

Nótese que cuando R y S son complementarios, el valor de S es igual al valor de Q y el valor de R es igual al valor de Q’. Tomando esto en consideración, se acostumbra invertir de la siguiente manera las terminales de entrada para que estén de acuerdo con el orden en la figura de los valores que toman las terminales de salida:

Frecuentemente, este circuito se encierra en una “caja negra” representándosele de la siguiente forma:

Este bloque se conoce comúnmente como el Flip-Flop R-S, aunque también se le conoce ampliamente como un R-S latch, y desempeña un papel importante en los circuitos lógicos.

El comportamiento de un flip-flop R-S (y de hecho el comportamiento de cualquier circuito lógico secuencial capaz de pasar de un estado estable a otro) puede ser descrito con un diagrama de tiempos como el siguiente, en el cual el paso del tiempo ocurre de izquierda a derecha:

En este diagrama de tiempos, al principio de la “acción” ambas terminales de entrada S y R están puestas a un valor de “1” lógico, mientras que se supone que la salida Q se encuentra en un estado estable de “0”. Como podemos ver, la terminal R recibe un descenso de “1” a “0” seguida de un ascenso que la regresa a su valor de “1”, pero esto no produce efecto alguno en la salida puesto que para ello es la terminal S la que tiene que ser activada. Esto es precisamente lo que se lleva a cabo a continuación, y podemos ver que al caer S de “1” a “0” la salida Q cambia de inmediato de “0” a “1”. Tras esto, la terminal S es llevada de “0” a “1”, y nuevamente se le aplica otro descenso, pero en esta ocasión ya no tiene efecto alguno sobre la salida Q, su efecto ya se dejó sentir anteriormente. Por último, con la salida Q ajustada a “1”, la terminal R es llevada de “1” a “0”, y en esta ocasión si produce un efecto inmediato, “reajustándose” la salida de Q a un valor de “0”. Este diagrama de tiempos resume prácticamente todas las condiciones posibles que describen el comportamiento del circuito, como debe hacerlo un buen diagrama de tiempos.

Una manera de mostrar dinámicamente la acción de un flip-flop R-S construído con bloques lógicos NAND en mediante el siguiente gráfico animado con foquitos encendidos indicando un valor lógico de “1” y foquitos apagados indicando un valor lógico de “0”:

Podemos construír un flip-flop con bloques NAND, o podemos procurarlo ya construído en un componente como el circuito integrado 4044, el cual incluye cuatro flip-flops NAND por el precio de uno solo:

PROBLEMA: Usando álgebra Boleana, encontrar expresiones para las salidas en función de las entradas, simplificando las expresiónes resultantes lo más que se pueda, para un Flip-Flop construído con bloques NAND. Asimismo, constrúyase una Tabla de Verdad para el circuito usando las expresiones obtenidas.

Trazando el flujo de señales para un flip-flop construído con bloques NAND, se ve que las salidas deberán ser como se muestra en el siguiente diagrama:

Las expresiones Boleanas para las salidas son:

Introduciendo cada expresión en la otra para tener las salidas en función de las entradas R y S exclusivamente:

Usando la ley de DeMorgan A · B = A + B para simplificar ambas expresiones:

Con las expresiones anteriores podemos introducir valores de R y S para construír una Tabla de Verdad:

R=0, S=0:

Q = 0 + 0 • QR=0, S=1:

Q= 1

Q = 0 + 0 • Q

Q = 1

Q = 0 + 1 • QR=1, S=0:

Q = 1 + Q

Q = 1

Q = 1 + 0 • Q

Q = 0 + 0

Q = 0

Q = 1 + 0 • QR=1, S=1:

Q = 0 + 0

Q = 0

Q = 0 + 1 • Q

Q = 1 + Q

Q = 1

Q = 1 + 1 • QLlamando al estado en el cual los valores de Q y Q no son complementarios (R=0 y S=0) un estado no-definido, podemos construír la Tabla de Verdad con la información obtenida:

Q = 0 + Q

Q = Q

Q = 1 + 1 • Q

Q = 0 + Q

Q = Q

Esta es la misma Tabla de Verdad que la obtenida en el problema anterior, excepto que aquí se obtuvo por una vía mucho más rápida, sin tener que probar todas las combinaciones posibles de “unos” y “ceros” en las entradas R y S y en las salidas Q y Q. Nuevamente, la enorme efectividad del álgebra Boleana como herramienta de simplificación muestra su potencia matemática.

PROBLEMA: Usando álgebra Boleana, encontrar expresiones para las salidas en función de las entradas, simplificando lo más que se pueda, para el siguiente flip-flop R-S construído con bloques NOR:

Asimismo, constrúyase una Tabla de Verdad para el circuito usando las expresiones obtenidas.

Trazando el flujo de señales para un flip-flop R-S construído a base de bloques NAND, se ve que las salidas deberán ser como se muestra a continuación:

Las expresiones Boleanas para las salidas son:

Introduciendo cada expresión en la otra para tener las salidas en función de las entradas R y S exclusivamente:

Usando la ley de DeMorgan A + B = A · B para simplificar ambas expresiones:

Con las expresiones anteriores podemos introducir valores de R y S para construír una Tabla de Verdad:

R=0, S=0:

Q = 0 (0 + Q)R=0, S=1:

Q= 1 • Q

Q= Q

Q = 0 (0 + Q)

Q= 1 • Q

Q = Q

Q = 0 (1 + Q)R=1, S=0:

Q = 1 (1)

Q = 1

Q = 1 (0 + Q)

Q = 0 (Q)

Q = 0

Q = 1 ( 0 + Q)R=1, S=1:

Q = 0 (Q)

Q = 0

Q = 0 (1 + Q)

Q = 1 (1)

Q = 1

Q = 1 (1 + Q)Llamando al estado en el cual los valores de Q y Q no son complementarios (R=1 y S=1) un estado no-definido, podemos construír la Tabla de Verdad con la información obtenida:

Q = 0 (0)

Q = 0

Q = 1 (1 + Q)

Q = 0 (1)

Q = 0

Comparando esta Tabla de Verdad con la obtenida en el problema anterior para un flip-flop R-S construído con bloques NAND, encontramos que son casi idénticas excepto por una diferencia: mientras que para un flip-flop R-S construído con bloques NAND la condición en la cual el flip-flop entra en un estado indefinido está dada por R=0 y S=0, para el flip-flop R-S construído con bloques NOR la condición en la cual el flip-flop entra en un estado indefinido está dada por R=1 y S=1. Asimismo, la condición en la cual el flip-flop R-S construído con bloques NAND “recuerda” su estado anterior es R=1 y S=1, mientras que para el flip-flop construído con bloques NOR la condición en la cual el flip-flop “recuerda” su estado anterior es R=0 y S=0.

Podemos construír un flip-flop con bloques NOR, o podemos procurarlo ya construído en un componente como el circuito integrado 4043, el cual incluye cuatro flip-flops NOR por el precio de uno solo:

Podemos visualizar mejor el funcionamiento de un flip-flop R-S construido con bloques NOR mediante el siguiente gráfico animado con foquitos encendidos indicando un valor lógico de “1” y foquitos apagados indicando un valor lógico de “0”, empezando con una condición en la que el flip-flop R-S se encuentra en en el estado Q=0 y la aplicación de dos pulsos iniciales en la terminal R no producen cambio alguno, hasta que aplicamos un pulso en la terminal S que hace que el estado del flip-flop R-S cambie a Q=1 tras lo cual la aplicación de un nuevo pulso en la terminal S ya no produce cambio alguno, y es la aplicación de un pulso en la terminal de reseteo R la que devuelve al flip-flop R-S a su estado Q=0:

Sin duda alguna, el funcionamiento de un flip-flop R-S construido con bloques NOR es más intuitivo y más fácil de recordar que el funcionamiento de un flip-flop R-S construido con bloques NAND. Es por esta razón que, a menos de que se indique lo contrario, en todos los problemas restantes de aquí en adelante se utilizarán exclusivamente flip-flops R-S hechos con bloques NOR.

PROBLEMA: Construír un diagrama de tiempos para un flip-flop R-S construído con bloques NOR.

PROBLEMA: Encontrar las modificaciones externas requeridas por un flip-flop R-S hecho con bloques NAND para que se comporte como si fuera un flip-flop hecho con bloques NOR.

Requerimos un bloque que transforme las entradas del flip-flop hecho con bloques NAND en la manera como se muestra a continuación:

Tomando en cuenta las características del flip-flop R-S hecho con bloques NOR y los requerimientos del flip-flop hecho con bloques NAND, las entradas y salidas del bloque transformador (mostrado de color ciano) deben estar relacionadas según se muestra en la siguiente Tabla de Verdad de dos entradas y dos salidas, obtenida mediante la técnica de los minterms:

de la cual obtenemos las siguientes relaciones:

S = SERE + SERE

S = (SE + SE)RE

S = RE

R = SERE + SERE

R = SE(RE + RE)

R = SE

La configuración requerida toma entonces el siguiente aspecto:

Si encerramos todo esto dentro de una “caja negra” y se lo damos a un técnico para que haga las pruebas necesarias para determinar qué clase de flip-flop es, el técnico creerá que se trata de un flip-flop R-S hecho con bloques NAND. A menos de que sea un técnico realmente bueno y no se deje llevar tan sólo por las apariencias.

PROBLEMA: Analizar el siguiente circuito.

Para llevar a cabo el análisis, supóngase que inicialmente Bin=0, A=0 y Bout=0.

Con A=0 y Bin=0, las salidas del AND 1 y del AND 2 deben ser ambas “1”, entradas con las cuales el flip-flop R-S mantiene su estado de Bout=0. que aquí suponemos válido. Al tomar Bin el valor “1”, las salidas de los dos AND siguen siendo “1” y el flip-flop seguirá reteniendo su estado Bout=0. Esto es, no importa el valor que tome Bin, éste no podrá afectar al flip-flop mientras la terminal A permanezca en la condición A=0. Si el flip-flop tuviera una salida Bout=1, esta también permanecerá constante ante cambios de Bin siempre y cuando la terminal A permanezca en “0”.

Suponiendo que ahora la terminal A toma el valor de “1” observamos que las entradas al flip-flop serán complementarias y sus valores dependerán del valor que tome Bin. En este estado, si aplicamos un “1” a Bin, el AND 1 producirá una salida de “0” y el AND 2 producirá una salida de “1”, lo cual pondrá al flip-flop en el estado Bout=1. Removiendo el "1" de la terminal A primero y el “1” de la terminal Bin después, las salidas de los AND 1 y 2 serán “1”, con lo cual el flip-flop retendrá el valor Bout=1. Sin el “1” en la terminal A, no importa que valor tome Bin, la salida seguirá siendo Bout=1. Esto es, al activar la terminal de acceso A, el circuito conservará en su memoria (a la salida Bout) el valor que le hayamos aplicado a Bin durante el período de tiempo que duró activada la terminal A. Si el bit de entrada Bin es “0”, basta activar por un corto tiempo la terminal A para “grabar” dicho bit en el circuito, pudiendo leer el bit a la salida Bout cuantas veces se desee tiempo después de que se haya desactivado la terminal A. Si deseamos “grabar” el bit “1”, entonces lo ponemos en la terminal de entrada Bin y activamos la terminal de acceso A por un tiempo corto, después del cual el bit está disponible a la salida Bout para ser leído cuantas veces se desee. Este es básicamente un circuito para almacenar un bit de información por tiempo indefinido.

Un diagrama de tiempos ilustrando todas las combinaciones secuenciales posibles es el siguiente:

PROBLEMA: El RAM (la Memoria de Acceso al Azar). Supóngase que existe un arreglo rectangular de flip-flops ordenados en un acomodo rectangular de 3 por 5 cuadros, cada cuadro conteniendo un flip-flop. Ilustrar la manera en la cual se pueda localizar un flip-flop cualquiera en un momento dado. Ilustrar también la manera en la cual se puede introducir y saca información de dicho flip-flop.

El arreglo más probable sería el siguiente:

Supóngase que deseamos encontrar el elemento mostrado en la figura. Para ello bastará con activar las terminales que lo localizan, que en este caso equivale a poner X3=1 y Y4=1, dejando un “0” en todas las demás terminales.

Siguiendo la convención del problema anterior, Bout es el bit ya almacenado por un flip-flop seleccionado, mientras que Bin es el bit a ser almacenado por el flip-flop seleccionado.

Podemos ver en el diagrama que la terminal Bin va dirigida hacia cada elemento del arreglo rectangular, cada uno de los cuales será llamado célula básica o celda para nuestros propósitos, mientras que la terminal Bout viene conectada desde cada célula. Asimismo, la terminal “Escribir/Leer” está también conectada a cada célula.

El diagrama de una célula básica es el siguiente:

Dentro de cada célula estamos utilizando la configuración estudiada en el problema anterior (la cual tomamos como “caja negra” y no se muestra en detalle para simplificar este diagrama esquemático).

Empezamos suponiendo que para la célula arriba mostrada, X3=1 y Y4=1, esto es, estamos domiciliando dicha célula, la célula especificada por las "coordenadas" X3 y Y4. Esto implica que la salida del AND1 es “1”. Si otra célula fuese la localizada, entonces tendríamos Xn ó Yn ó ambos, con lo cual la salida del AND sería entonces “0”.

Para analizar el comportamiento de la célula básica, estudiamos dos casos diferentes:

a) La terminal R/W (Read/Write, que en español se traduce como "Escribir/Leer") está desactivada con un “0”. En este caso, la salida del AND 2 es “0”, lo cual implica que la terminal de acceso A está desactivada y la información contenida por el flip-flop (Bo) permanece inalterada. Al mismo tiempo, el AND 3 está activado y su salida Bo dependerá de la información Bo previamente almacenada en el flip-flop. Estamos, por lo tanto, leyendo información de la célula localizada. Esta es la función R (Read) de lectura.

b) La terminal R/W es activada con un "1". En este caso, la salida del AND 2 es “1”, lo cual implica que la terminal de acceso A está activada. La salida Bo del flip-flop (que es la salida Bo de la célula) dependerá del valor que tome Bi. Podemos, por lo tanto, escribir información en la célula localizada; esta es la función W (Write) de escritura, después de lo cual desactivamos la terminal R/W poniéndole nuevamente un "0" para poder preservar dicha información.

PROBLEMA: Una memoria RAM tiene una capacidad de 8 por 8 bits. ¿Cómo se puede seleccionar cada bit sin usar un gran número de terminales fuera del RAM?

Antes de continuar, identificaremos cada terminal de entrada de selección del RAM con un número binario diferente (al cual se le llamará “domicilio” o adresss) como se muestra a continuación:

No se ha mostrado en el diagrama la terminal bi-direccional de “Escribir/Leer” (Read/Write) con la cual se escribe un bit dentro de los flip-flops seleccionados. Obsérvese que en cada caso (domicilios horizontales, domicilios verticales) se escogió una numeración binaria ascendente tanto para los domicilios horizontales como para los verticales. Podemos añadir ahora un decodificador binario en cada lado para tener entonces el siguiente circuito:

Podemos observar que con este arreglo, el número de terminales requeridas para encontrar un determinado bit (o mejor dicho, un determinado flip-flop que está almacenando un bit que puede ser un “0” o un “1”) se reduce grandemente. En las figuras se ha mostrado el flip-flop identificado por las combinaciones A0A1A2=110 y A3A4A5=100 (o bien, por la palabra A0A1A2A3A4A5=110100, que es lo que comunmente se acostumbra usar.

El esquema de domiciliar cada una de las células básicas de una memoria RAM utilizando un arreglo rectangular y reduciendo el número de líneas empleadas para el domiciliamiento con la ayuda de un decodificador horizontal y un decodificador vertical es un concepto completamente general, independiente de la tecnología empleada, ya sea mediante núcleos de ferritas magnéticas o mediante semiconductores o mediante algún otro esquema que aún no ha sido descubierto:

En esta representación estamos introduciendo un nuevo concepto con el objetivo de simplificar los diagramas esquemáticos en los cuales varias líneas de conducción eléctrica que llevan información simultánea perteneciente a un mismo grupo de datos son representadas en conjunto como una sola flecha “gorda” en vez de las cuatro u ocho líneas que de otro modo tendrían que ser dibujadas independientemente sin que este exceso de líneas resulte en una mayor claridad de información. Esta “flecha gorda” que aparea datos pertenecientes a información del mismo género es conocida como bus, (posiblemente en similitud con la palabra inglesa con la cual se designa a los camiones públicos utilizados para transportar a varias personas a la vez). Así, el bus que tenemos a la derecha en la siguiente figura representa a las ocho líneas que tenemos a la izquierda de la misma:

PROBLEMA: Ilustrar la forma de conectar varias RAM con una capacidad de 4 por 4 bits cada una para almacenar palabras de 3 bits. ¿Cuál es la capacidad total de memoria del sistema expresada en bits? ¿Cuántas palabras se pueden almacenar?

Puesto que se quiere almacenar palabras de 3 bits de extensión, se requieren tres RAM. Debido a que el arreglo de cada RAM es simétrico (o sea, de 4 por 4 bits) y a que la capacidad horizontal (y la vertical) es una potencia de 2n siendo n=2, podemos usar decodificadores para así tener la siguiente configuración:

Cada RAM tieen una capacidad de 4x4=16 bits. Puesto que se están usando tres memorias RAM de 4 por 4 bits de capacidad cada una, la capacidad total de almacenamiento será de 16 bits por 3, o sea de 48 bits (una capacidad modesta cuando en los inicios del 2007 las capacidades de las memorias RAM a la venta para las computadoras personales de escritorios alcanzaban una capacidad de dos gigabytes, dos mil millones de bits). Obsérvese que si cada RAM tiene integrados sus propios decodificadores (esta es la práctica usual) sin necesidad de que un ingeniero o técnico los tenga que añadir a algún diseño, el arreglo del circuito se simplifica enormemente como se muestra a continuación:

La simpleza de esta configuración sobre la anterior es obvia. La ventaja de usar bloques RAM con decodificadores incluídos en las RAM se hace más obvia aún cuando la cantidad de bloques RAM usados y la capacidad de los mismos va en aumento.

PROBLEMA: Un fabricante anuncia un nuevo tipo de memoria RAM ultra-rápida de 1024 bits hecho a base de tecnología óptica. ¿Cuál es la configuración funcional más probable para tal circuito?

Lo más probable es que sea una RAM de tipo simétrico con las células básicas de información acomodadas en un arreglo rectangular, formada por n bits de cada lado. Podemos, basados en esta información, obtener el número de bits laterales:

n ∙ n = 1024

n² = 1024

n = 32

n² = 1024

n = 32

La RAM parece ser una RAM de 32 bits por 32 bits. Lo más probable también es que use decodificadores en ambos lados con el propósito de reducir las líneas externas de alambrado necesarias para poder llegar a cada célula de información. La extensión de la palabra requerida en cada lado la podemos encontra de la siguiente manera:

2n = 32

log [ 2n ] = log(32)

n ∙ log(2) = log(32)

n = (log 32)/(log 2)

n = (1.50515)/(.30103)

n = 5

n ∙ log(2) = log(32)

n = (log 32)/(log 2)

n = (1.50515)/(.30103)

n = 5

El resultado nos dice que una palabra de tan sólo cinco bits contendrá 32 combinaciones posibles de “unos” y “ceros”.

La RAM tendrá entonces la siguiente configuración:

El “bit” a ser leído con la operación de lectura R (poniendo un “0” en la terminal R/W) será leído de la terminal Bo, mientras que el “bit” a ser escrito con la operación de escritura W (poniendo un “1” en la terminal R/W) será puesto en la terminal Bi.

PROBLEMA: La ROM (Memoria de Lectura Unicamente). Analizar el siguiente circuito construyendo una Tabla de Verdad para el mismo.

El primer paso para analizar este tipo de circuito es introducir todas las combinaciones posibles de “unos” y “ceros” en las terminales de entrada A, B y C. Por ejemplo, con la combinación AB=00, únicamente se activa la línea L1. De la misma manera, con cada una de las combinaciones restantes se activa únicamente una de las líneas L2, L3 y L4. No nos debe llevar mucho tiempo el reconocer que lo que tenemos dentro del recuadro de línea roja es nada menos que un decodificador. Las salidas H1, H2, H3 y H4 se pueden obtener de inmediato de los ORs sabiendo que únicamente una de las líneas L puede estar activada en un momento dado. Tomando esto en consideración, la Tabla de Verdad obtenida será como la que se muestra a continuación:

Podemos ver que cada combinación de “unos” y “ceros” a la entrada siempre producirá la misma combinación de “unos” y “ceros” que le corresponda a la salida a dicha entrada, determinado por las conexiones internas en el circuito. Esto, en cierta forma, es equivalente a una “memoria”, la cual está contenida dentro del recuadro de línea verde. Sin embargo, este tipo de memoria es diferente a las demás en el sentido de que únicamente se pueden leer palabras binarias de la misma. No se pueden grabar palabras nuevas en este tipo de memoria sin cambiar el alambrado interno del circuito. Es por esto que esta memoria es conocida comúnmente como Memoria de Lectura Unicamente (Read Only Memory ó ROM), ya que únicamente se pueden leer palabras de este memoria, no se pueden grabar palabras en la misma.

El ROM ofrece una configuración almacenada de “unos” y “ceros” que puede ser utilizada de la misma manera que un programa almacenado en la memoria de una computadora digital. La secuencia de eventos lógicos puestos en movimiento por esta configuración almacenada de datos recibe el nombre de microprograma. Asismismo, cada evento lógico especificado en los domicilios de un microprograma recibe el nombre de microinstrucción.

PROBLEMA: Tomando en cuenta el circuito del problema anterior, diseñar un ROM que posea la siguiente Tabla de Verdad:

La configuración pedida tiene el siguiente aspecto:

PROBLEMA: Describir la forma en la cual trabaja la Memoria ROM cuyo diagrama esquemático es el siguiente:

La forma (simbólica) en la cual trabaja esta memoria ROM de acuerdo con lo que podemos leer en este diagrama esquemático es la siguiente:

Cuando todos los interruptores eléctricos en el extremo izquierdo del diagrama están abiertos tal y como se muestra arriba, no entra ningún voltaje (ningún “1”) en ninguna de las terminales de entrada A0, A1, A2 y A3, siendo por lo tanto la entrada “0” en todas ellas. Así, cuando la palabra de entrada es A0A1A2A3=0000, accesamos de la memoria ROM su contenido puesto en una de sus “celdas”, que es el dato 4D (dado en notación hexadecimal, equivalente a 01001101 en notación binaria). Este dato es puesto en las líneas de salida del ROM como el byte:

D7D6D5D4D3D2D1D0= 01001101

tal y como lo muestra el diagrama. Si queremos accesar otro contenido dentro del ROM, por ejemplo el contenido que está puesto bajo el domicilio A0A1A2A3=0011 entonces cerramos los interruptores eléctricos que corresponden a las líneas de entrada A0 y A1, con lo cual el voltaje que tomamos como “1” pasa directamente a dichas líneas. Junto con los ceros en las demás entradas, esto pone el domicilio 3 (0011) en la entrada A0A1A2A3, lo cual accesa el contenido en el domicilio 3 que es 6D, el cual será puesto a la salida del ROM.

Este ROM tiene capacidad suficiente para almacenar 16 bytes.

Este circuito fue tomado de la página Internet de Educypedia. La acción animada de este ROM “trabajando” se puede ver yendo al siguiente domicilio:

http://www.ibiblio.org/kuphaldt/socratic/output/animation_ROM_memory_fast.gif

PROBLEMA: El código ASCII. Una de las desventajas del indicador luminoso de 7 segmentos es que no se pueden representar las letras del alfabeto en el mismo. Este problema se soluciona empleando una matriz (arreglo rectangular) de 5 por 7 diodos LED, cada uno en forma de punto. Representar la expresión A+B usando este tipo de indicadores. Bajo el código ASCII, se pueden representar hasta 64 caracteres diferentes si se usa un ROM para almacenar la combinación particulas de "unos" y "ceros" correspondientes a cada caracter. ¿Cuál es la capacidad total en bits requerida del ROM? ¿Cuál es su configuración más probable?

Usando tres matrices de diodos LED indicadores, la expresión A+B tendrá un aspecto como el siguiente:

Para representar cada caracter se requieren 7 por 5 bits, o sea 35 bits. Puesto que en el código ASCII hay un total de 64 caracteres, o sea 64 combinaciones diferentes de “unos” y “ceros”, se concluye que la capacidad total de almacenamiento requerida del ROM es de 35x64 = 2240 bits.

Puesto que 64 es un múltiplo de 2n, en lugar de usar 64 líneas diferentes para obtener cada caracter se puede usar identificación binaria para obtener cada caracter usando un decodificador. Incluyendo el decodificador en el ROM, vemos que el número n de líneas requeridas será:

2n = 64

log(2n) = log(64)

n ∙ log2 = log64

n = (log64)/(log2)

n = (1.80618)/(.30103)

n = 6

log(2n) = log(64)

n ∙ log2 = log64

n = (log64)/(log2)

n = (1.80618)/(.30103)

n = 6

Requerimos de 6 líneas de entrada al decodificador del ROM. Una configuración posible para el ROM requerido sería la siguiente:

La letra A está representada a la salida del ROM como ejemplo del funcionamiento del mismo.

PROBLEMA: Un ROM usado en conjunción con el código ASCII para almacenar 64 caracteres representados cada uno de ellos por una matriz de 5 por 7 puntos invariablemente posee 35 terminales de salida junto con 6 terminales de entrada. ¿Cómo se puede simplificar el elemento?

Para lograr una reducción del número de líneas requeridas, modificamos el ROM del problema anterior añadiendo compuertas a la salida de información de cada columna para así tener la siguiente configuración (cada una de las compuertas está mostrada de color amarillo, y en cada una de ellas es necesario poner un "1" en cada terminal C para permitir el flujo de la información a través de la compuerta):

El circuito anterior frecuentemente se simplifica de la siguiente manera:

En este caso, se escogió la salida producida cuando la letra B ha sido seleccionada. El indicador alfanumérico luminoso presentará el siguiente aspecto (los puntos LED no activados correspondientes a la letra B están distinguidos con color amarillo pálido) cuando la columna 3 de la matriz está siendo activada (los puntos LED correspondientes a la columna activada están distinguidos con color rojo):

Antes que nada, se puede observar que un ROM que poseía originalmente 35 terminales de salida posee únicamente 7 a cambio de añadir 5 terminales de entrada (las correspondientes a los selectores de columnas Ci). ¡Este es un ahorro substancial de alambrado! De la misma manera, el indicador luminoso que requería 35 terminales de entrada requiere ahora únicamente de 12. Para representar un caracter ASCII bajo esta técnica (después de que ha sido seleccionado en la sección de domicilios del ROM) se va activando cada una de las terminales Ci sucesivamente tanto en el ROM como en el indicador, con la suficiente rapidez para que bajo el fenómeno conocido como la persistencia visual (que ha hecho posible la televisión y la cinematografía) el indicador dé la impresión de estar representando un caracter fijo e inmóvil, aunque no sea así. Este método mediante el cual se pueden reducir considerablemente las líneas requeridas para la interconexión de los elementos de un sistema recibe el nombre de multiplex y puede reducir considerablemente la complejidad de los circuitos, según se puede apreciar en este problema.

Es importante agregar que, aún con la técnica del multiplex, el consumo de energía requerido por los indicadores luminosos LED eventualmente los hizo imprácticos para aplicaciones portátiles de bolsillo tales como los relojes de mano (los primeror relojes de mano digitales que aparecieron en el mercado fueron hechos a base de diodos emisores de luz LED, pero estos no daban una indicación continua de la hora todo el tiempo, había que oprimir un botón para que apareciera la lectura en la carátula). Esta es la razón por la cual en muchas aplicaciones portátiles los diodos emisores de luz fueron reemplazados por otra tecnología que requiere un consumo mucho menor de energía por estar basada no en la emisión de luz proveniente de un semiconductor sino en la reflexión y absorción de la luz en base a carátulas de cristal líquido (liquid crystal display ó LCD):

en las cuales la transparencia o la opacidad del punto seleccionado dependerá de la aplicación de un voltaje (un "1"):

y las cuales pueden proporcionar un nivel de detalles bastante aceptable para muchas aplicaciones portátiles, como en la siguiente muestra tomada de la carátula de una cámara digital:

De cualquier modo, y es importante señalarlo, aún las carátulas de cristal líquido utilizan en forma intensiva la técnica del multiplex.

PROBLEMA: Se desea almacenar el número pi (π = 3.141592654) en forma permanente dentro de una calculadora electrónica usando el sistema BCD. Describir las características del ROM utilizado. Ignorar el punto decimal.

Designando al dígito en el extremo izquierdo del número pi (π) como el primero, la Tabla de Verdad indicando el número BCD requerido para cada dígito será como sigue:

Puesto que para representar cada dígito en el sistema BCD se requieren 4 terminales de salida, para leer los diez dígitos se requerirán 40 terminales de salida en el ROM, lo cual representa una cantidad intolerable de alambrado. Usando la técnica del multiplex (MUX) estudiada en un capítulo previo, podemos simplificar el ROM haciendo que la activación de un dígito en particular nos dé a la salida del ROM el número BCD correspondiente a dicho dígito, como se muestra a continuación:

De este modo, al activar la terminal correspondiente al primer dígito, en las cuatro terminales de salida se tendrá el número BCD 0011 correspondiente al dígito 5, con lo cual la salida , equivalente al número decimal 3, el primer dígito del número π. Al activar la terminal correspondiente al segundo dígito, en las cuatro terminales de salida se tendrá el número BCD 0001, equivalente al número decimal 1, el segundo dígito del número π. Es obvio que para sacar el número π del ROM habrá que activar cada terminal “dígito” en una secuencia ordenada y continua. En el diagrama se muestra activada la quinta terminal del ROM con lo cual la salida toma la condición 0101, equivalente al número decimal 5, el quinto dígito del número π.

El número e (= 2.718281828) también se puede almacenar en una calculadora electrónica en forma permanente usando la técnica arriba descrita. Y de hecho, así es como se almacenan los números π y e en una calculadora electrónica de bolsillo, usando una memoria ROM. Por esto las calculadoras de bolsillo nunca olvidan estos dos números célebres.

PROBLEMA: Ocasionalmente, es deseable tener a la mano un ROM cuyo contenido pueda ser programado para alguna aplicación especial en un proyecto particular. Esto se logra diseñando un ROM con fusibles internos, habiendo tantos fusibles como bits usados. Teniendo esto en mente, diseñar un ROM programable de dos entradas y tres salidas.

Puesto que la unidad tiene dos entradas, las combinaciones posibles de “unos” y “ceros” son cuatro, las cuales son procesadas por un decodificador tomando cada combinación y activando a la vez una sola línea a la salida del mismo. El circuito presentará el siguiente aspecto:

Este tipo de ROM programable es conocido comúnmente como la PROM (Programmable Read Only Memory). Para programar un PROM, cada fusible se tiene que hacer estallar individualmente, con un tiempo mínimo de enfriamiento entre cada estallamiento ya que se genera cierta cantidad de calor dentro del circuito.

PROBLEMA: ¿Cuáles serán las palabras binarias de salida producidas por la siguiente memoria PROM que ya ha sido programada y que por lo tanto se puede considerar convertida ya a una memoria ROM?

Es importante recordar que sólo una de las líneas A0, A1 y A2 puede estar activada a la vez. Empezamos por ver que en el primer renglón ninguno de los fusibles-diodos ha sido “quemado”, de modo que cuando la línea A0 está poniendo un “1” en el primer renglón ese “1” pasa directamente a las tres columnas D2, D1 y D0 que la cruzan. Entonces la salida será D2D1D0=111 para A0=1. En el segundo renglón, el fusible-diodo intermedio ha sido "quemado" y ya no está presente para pasar a la columna D1 un “1” puesto en el renglón A1. Entonces la salida será D2D1D0=101 para A1=1. Por último, en el tercer renglón, el fusible-diodo alineado con la columna D0 ha sido "quemado" y ya no está presente para pasar a la columna D0 un “1” puesto en el renglón A2. Entonces la salida será D2D1D0=110 para A2=1.

PROBLEMA: ¿Cuáles serán las salidas S1 y S2 producidas por la siguiente memoria en función de las entradas a, b, c y d? ¿De qué tipo de memoria se trata?

En el primer renglón correspondiente a la entrada a, el tercer diodo-fusible de izquierda a derecha ha sido “vaporizado” (del mismo modo que en el segundo renglón correspondiente a la entrada b el segundo diodo-fusible ha sido “quemado”; y que en el tercer renglón correspondiente a la entrada c tanto el primer fusible como el cuarto fusible han sido quemados; y que en el cuarto renglón correspondiente a la entrada d todos los diodos-fusibles excepto el cuarto han sido quemados); y por este motivo la línea a no podrá poner nada en la tercera columna cuando la entrada a tenga el valor de “1” (del mismo modo que la línea b no podrá poner nada en la segunda columna; y que la línea c no podrá poner nada ni en la primera columna ni en la cuarta columna; y que la línea d no podrá poner nada más que en la cuarta columna). Fijándonos bien en la acción eléctrica de los componentes, podemos ver que para que haya una salida de “1” en S1 es necesario que tanto a como b tengan ambas una entrada de “1” (esta es una operación AND), o bien que tanto b como c tengan una entrada de “1” (esta es otra operación AND). Cualquiera de estas dos posibilidades, ya sea ab o bc, ponen un “1” en la salida S1, lo cual equivale a una combinación OR de ambas operaciones. El análisis para la salida S2 es similar.

Las dos salidas Boleanas del circuito serán por lo tanto:

S1 = ab + bc

S2 = ac + abd

S2 = ac + abd

No resulta difícil ver que esta memoria consta de dos matrices, la primera es la matriz superior que está atravesada por las líneas (renglones) a, b, c y d, mientras que la segunda matriz es la matriz inferior que está atravesada por las líneas (renglones) S1 y S2. Y ya vimos que tanto en la matriz superior como en la matriz inferior se “quemaron” varios fusibles, lo cual significa que tanto las entradas como las salidas son programables. Entonces la memoria es un PLA.

PROBLEMA: ¿Qué es una línea de retardo?

Considérese la siguiente configuración:

Aparentemente, la combinación arriba mostrada no lleva a cabo ninguna función útil, ya que la información que es invertida por el primer inversor vuelve a ser invertida por el segundo inversor obteniéndose así a la salida la información original a la entrada sin cambio alguno.

Sin embargo, un momento de reflexión nos indica que tenemos a la mano una variable que no habíamos considerado hasta ahora. Sabemos de antemano que al introducir información binaria a la entrada de un inversor, es físicamente imposible que aparezca instantáneamente la respuesta a la salida del mismo. En efecto, antes de llegar al límite impuesto por la velocidad de la luz, entran en juego otros parámetros físicos relacionados con las cuestiones eléctricas (tales como la inductancia y la capacitancia) que ponen un límite a la velocidad de respuesta del inversor. Esto es, hay un retardo de tiempo introducido por el inversor. Dependiendo de la familia lógica utilizada (véase el Suplemento # 1: Las familias lógicas), cada circuito integrado tendrá un retardo en la propagación de la señal desde su entrada hasta su salida conocido en las especificaciones técnicas como retardo de propagación (propagation delay). A manera de ejemplo, para un inversor NOT disponible en un circuito integrado TTL 7404, el retardo de propagación en promedio es de 10 nanosegundos, y para un inversor NOT disponible en un circuito integrado CMOS 4049 el retardo de propagación en promedio es de 25 nanosegundos. Hasta ahora se había considerado este retardo de tiempo como despreciable. Sin embargo, al conectar dos inversores en serie, este retardo de tiempo se vuelve el doble del retardo original.

Configuraciones como la anterior que no llevan a cabo ningún procesamiento de información pero que introducen un retardo de tiempo T a la información a su entrada se conocen comúnmente como línea de retardo y se pueden representar de la siguiente manera:

La doble banda indica el lado en el cual se introduce la información en la línea de retardo. El retardo de tiempo T se indica dentro de la línea de retardo (100 microsegundos, 10 nanosegundos, etc.).

Básicamente, el funcionamiento es sencillo. Si se introduce un “1” a la entrada de la línea de retardo, después de un tiempo T aparecerá un “1” a la salida de la misma. Y si se introduce un “0” en la línea de retardo, después de un tiempo T aparecerá un “0” a la salida de la misma.

Además de los retardos inherentes en los circuitos integrados utilizados para construír sistemas digitales, existen varias formas de obtener retardos de tiempo en la propagación de una señal introduciendo un mínimo de distorsión en la misma, tales como el uso de bobinas como la que se muestra a continuación capaz de producir un retardo de 390 nanosegundos:

Y a continuación tenemos la línea de retardo ADL CS344 que puede producir un retardo constante de 64 microsegundos:

Es muy importante aclarar antes de continuar adelante que las líneas de retardo tienen poco uso en la construcción de sistemas digitales de uso común, excepto para aplicaciones muy especializadas. La línea de retardo es útil en el estudio conceptual de los multivibradores que se pueden construír utilizando circuitos lógicos, y un retardo puede ser producido de modo mucho más económico utilizando una resistencia R y un condensador C cuya constante de tiempo RC en combinación con un temporizador (timer) como el 555 (véase el Suplemento # 8: El temporizador 555) puede ser utilizada para construír multivibradores de todo tipo.

Normalmente, los retardos de tiempo son un efecto sumamente desagradable que los ingenieros de diseño tratan de reducir al mínimo con el fin de tratar de obtener la máxima velocidad posible de un sistema digital (el mejor ejemplo que se puede citar son las computadoras personales de escritorio, cuyas velocidades de procesamiento están limitadas precisamente por estos retardos de tiempo). Sin embargo, para construír los multivibradores que serán tratados en los siguientes problemas, la introducción de retardos de tiempo se vuelve prácticamente una necesidad.

PROBLEMA: Diseñar un multivibrador mono-estable utilizando un flip-flop R-S y una línea de retardo.

El diseño deseado se muestra a continuación:

Para analizar este diseño, suponemos que el flip-flop R-S está inicialmente en la condición R=0, S=0 y Q=0.

Al aplicar un pulso (o un “1”) de corta duración en la terminal “gatillo” (trigger), el flip-flop R-S entra en el estado Q=1 en donde permanece después de desaparecer el pulso. Al tomar la terminal de "Salida" el valor Q=1, se coloca al mismo tiempo un “1” a la entrada de la línea de retardo. Transcurrido un tiempo T, este “1” aparece a la salida de la línea de retardo, lo cual a su vez hace que R=1. Puesto que el pulso en la terminal "gatillo" fue de corta duración, al tomar R el valor de “1” encontramos que S ya tiene el valor “0”. Con la condición R=1 y S=0, el flip-flop R-S regresa automáticamente al estado Q=0. Este estado Q=0 pone un “0” en la línea de retardo que después de un tiempo T vuelve a dejar al flip-flop R-S en su estado original R=0, S=0 y Q=0.

Un diagrama de tiempos ilustrando la acción sería como el siguiente:

Nótese que el ancho de pulso de la señal “gatillo” siempre debe ser menor que el ancho de la señal de salida para evitar poner al flip-flop en el estado no-definido R=1 y S=1.

El multivibrador monoestable también es conocido como el "multivibrador de un disparo" (one-shot).

PROBLEMA: A continuación se muestran las características de un elemento conocido como el "medio-monoestable":

Según se puede observar, la característica fundamental del medio-monoestable es que el ancho de pulso a la salida tiene una duración menor que el ancho de pulso a la entrada. Tomando en cuenta lo anterior, diseñar un medio-monoestable.

Un diseño posible es el siguiente:

Supongamos que la terminal “gatillo” está inicialmente en la condición “0”. La salida de la línea de retardo será también “0” al estar siendo alimentada con el “0” del “gatillo”, lo cual producirá un “1” a la salida del inversor. Las entradas del AND serán por lo tanto “1” y “0”.

Al aplicar un “1” a la terminal “gatillo”, las dos entradas al AND serán “1” y la salida de la configuración tomará el valor de “1”.

Transcurrido un tiempo T, el “1” a la entrada de la línea de retardo aparecerá a la salida del mismo, produciendo a su vez un “0” a la salida del inversor. Las entradas al AND serán entonces “0” y “1”, con lo cual la salida del AND tomará el valor de “0”.

Nótese que para obtener otro pulso de duración T a la salida del medio-monoestable, es necesario regresar la terminal “gatillo” a la condición "0", para así poder estar en condiciones de volver a “disparar” el medio-monoestable.

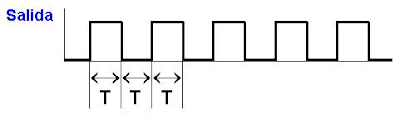

PROBLEMA: Analizar el comportamiento del siguiente circuito:

Suponemos que la salida es inicialmente Q=0. Esto a su vez implica que S=0 y R=1, considerando que las entradas al flip-flop R-S son complementarias debido a la acción del inversor. Tenemos entonces que Q=1, lo cual pone un “1” a la entrada de la línea de retardo.

Transcurrido un tiempo T, el “1” a la entrada de la línea de retardo aparece a la salida del mismo, lo cual produce las condiciones S=1 y R=0. Esto ocasiona que el flip-flop R-S cambie al estado Q=1.

Al tomar el flip-flop R-S el estado Q=1, entonces Q=0, lo cual pone un “0” a la entrada de la línea de retardo. Transcurrido un tiempo T, el “0” a la entrada de la línea de retardo aparece a la salida del mismo, lo cual produce las condiciones S=0 y R=1. Esto ocasiona que el flip-flop R-S regrese al estado Q=0.

Este proceso se repite indefinidamente.

Notamos, por lo tanto, que el circuito tiene dos estados inestables, Q=0 y Q=1.

Este circuito es básicamente un multivibrador astable de salida simétrica. La característica más interesante de esta configuración que la distingue de todas las demás estudiadas en esta obra es que no tiene entradas. Solo tiene una salida. En efecto, este es un bloque autosuficiente que puede generar por sí solo un tren de pulsos para su uso subsecuente en circuitos lógicos. La salida del mismo tendrá el siguiente aspecto en un diagrama de tiempos:

Podemos ver que el período de la onda cuadrada será 2T y que la frecuencia de la misma será f.=.1/2T.

PROBLEMA: Supóngase que a la entrada de la siguiente configuración se introduce un pulso con una duración de tiempo t=T/2. Obtener los diagramas de tiempo de las salidas A, B y C con respecto al pulso de entrada.

Los diagramas pedidos se muestran a continuación:

Al introducir un pulso de duración t en la terminal de entrada, éste aparece en la terminal A después de transcurrido un tiempo T marcado por la línea de retardo. A la vez, este pulso es introducido en la segunda línea de retardo. Transcurrido otro tiempo T aparecerá en la terminal B. Después de haber transcurrido otro tiempo T, el pulso aparecerá finalmente en la terminal C.

Esta configuración en la cual se produce una sucesión de pulsos en terminales consecutivas, ocurriendo únicamente un pulso a la vez, es conocida como Contador de Anillo y desempeña un papel importante en el diseño de computadoras digitales.

Obsérvese que si inmediatamente después de haber introducido el pulso a la entrada de la configuración se conecta la terminal C a la terminal de entrada, esta puede trabajar por sí sola produciendo pulsos por tiempo indefinido. Tenemos entonces lo que se llama un Oscilador de Anillo.

Aunque el diseño de un Contador de Anillo basado en el uso de líneas de retardo teóricamente puede funcionar, en la práctica esto se consideraría como un diseño pésimo, ya que no hay forma de ejercitar algún tipo de control sobre el deterioro que vaya teniendo el pulso como tampoco hay forma de garantizar un control preciso de los tiempos predichos teóricamente. Un Contador de Anillo mucho más confiable y seguro sería aquél cuyo diseño esté basado en bloques lógicos secuenciales bajo la acción directa de la señal de un pulso de reloj maestro, tales como los que serán tratados precisamente en el siguiente capítulo.

PROBLEMA: ¿Cuáles son los problemas potenciales que puede ocasionar en un circuito lógico construído con una variedad de funciones lógicas la presencia de un retardo de tiempo inherente en la respuesta de cada una de las funciones lógicas empleadas?

Considérese el siguiente circuito:

Si este circuito fuera un circuito ideal, sin retardos de tiempo en ninguno de los componentes,

entonces su comportamiento sería sencillo: con una entrada de “0” la salida del mismo debe ser

“0”, y al ponerle una entrada de “1” su salida debe seguir siendo “0”. Teóricamente, este circuito no debe producir salida alguna cualesquiera que sea el valor a su entrada. Sin embargo, la situación cambia cuando consideramos el retardo de propagación introducido por el bloque NOT, denominado en el diagrama como Δt1. La señal a la salida del NOT no cae instantáneamente de “1” a “0” cuando la entrada A toma el valor de “1”. Esto ocasiona que por un lapso breve de tiempo la salida del AND no será “0” sino “1”, manifestado como un pulso. El bloque AND introduce su propio retardo de tiempo Δt2 en dicho pulso, de modo tal que el pulso aparecerá a la salida del mismo un tiempo Δt1+Δt2 después. El problema es que dicho pulso, no anticipado y no deseado, puede introducir efectos erráticos inesperados en lo que de otra manera sería un buen diseño. El problema se origina en el hecho de que por el retardo de tiempo introducido por el NOT, se origina una carrera (race) entre las dos señales A y A que llegan a las dos entradas del AND, lo cual a su vez crea una condición de riesgo inesperado (hazard) por la presencia del pulso no-deseado.

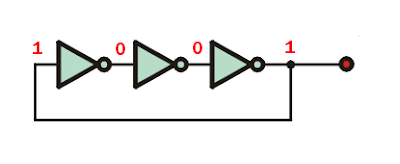

En el siguiente diagrama en el cual utilizamos un NOR en lugar de un AND tenemos una condición similar en la cual la duración del pulso no-deseado es mayor aún por el efecto combinado de tres NOTs (actuando como una línea de retardo) conectados en cascada uno tras el otro, triplicando el retardo de propagación introducido por cada uno de ellos:

El siguiente circuito muestra una condición aún más seria:

Primero llevaremos a cabo un análisis estático, sin consideración alguna del factor tiempo.

Supóngase primero que este es un circuito lógico ideal sin retardo alguno en la propagación de la señal a través de cada NOT. Supóngase ahora que la salida del último NOT (en el extremo derecho) es de “0”. Esto pone un “0” a la entrada del primer NOT (en el extremo izquierdo), el cual “instantáneamente” es puesto a su salida como un “1”, el cual entra al segundo NOT y sale del mismo también “instantáneamente” como un “0”. Este “0” es invertido por el tercer NOT y sale del mismo como un “1”. Pero habíamos supuesto que la salida del tercer NOT era “0”. Claramente esta es una condición incompatible.

¿Entonces qué es lo que sucedería si tratáramos de construír este circuito?

En este caso, no tenemos necesidad de preocuparnos por la situación teórica ideal (la cual trasladada al terreno de las matemáticas puras y al terreno de la lógica nos conduce a una paradoja), porque al momento de construír este circuito lo tenemos que hacer necesariamente con componentes físicos reales, los cuales siempre tienen un retardo de tiempo en la propagación de la señal desde su entrada hasta su salida.

Ahora llevaremos a cabo un análisis dinámico tomando en cuenta lo que va ocurriendo conforme el tiempo va avanzando.

Supóngase que el retardo de propagación en todos los NOTs tiene una duración de un tiempo T. Nuevamente, supóngase que la señal a la salida del tercer NOT es “0” al inicio de un intervalo de un primer tiempo que llamaremos t1, el cual será de duración T. Esta salida de “0” estará también puesta en la entrada del primer NOT (suponemos que el tiempo de viaje de la señal a través del alambre conector del tercer AND al primer AND es despreciable en comparación con el tiempo de propagación de la señal a través de cada NOT), y después de un tiempo T (al finalizar el tiempo t1) este “0” aparecerá a la salida del primer NOT invertido como “1”. Al finalizar el primer tiempo t1, también el tercer NOT cambiará su salida a lo que tenía puesto a su entrada. Supóngase que tenía puesto un "1", lo cual a su vez implica que la salida del segundo NOT era “1”. Supóngase también que la entrada del segundo NOT era "1". Esto no posible de concebir para un NOT ideal, sin embargo, no es imposible para el caso de un NOT real porque si el segundo NOT tenía un “1” a su salida por haber tenido puesto un “0” previamente a su entrada, entonces al serle puesto un “1” a su entrada su salida no caerá de “1” a “0” hasta que no haya transcurrido un tiempo T. Así el segundo NOT, por considerar que tiene una entrada de “1” y una salida de “1”, se encuentra en una condición lógicamente anómala. Sobre estas consideraciones, al inicio del tiempo t1 la situación es la siguiente:

Al finalizar el tiempo t1 y comenzar el tiempo t2, transcurrido un tiempo T, el “0” puesto a la entrada del primer NOT pasa invertido a su salida como un “1”. Por otro lado, el “1” puesto a la entrada del segundo NOT pasa invertido a su salida como un “0”, con lo cual el segundo NOT deja de estar en una condición lógicamente anómala. Este “0” a la salida del segundo NOT es puesto de inmediato a la entrada del tercer NOT. Por su parte, el “1” que estaba puesto a la entrada del tercer NOT pasa invertido a su salida como un “0”, manteniéndose por lo tanto el tercer NOT sin cambio en su condición lógica. Pero esto pone ahora al tercer NOT en una condición lógicamente anómala, al tener un"0" en su entrada y un "0" en su salida:

Al finalizar el tiempo t2 y comenzar el tiempo t3, transcurrido un tiempo T, el “0” puesto a la entrada del primer NOT pasa invertido a su salida como un “1”. Por otro lado, el “1” puesto a la entrada del segundo NOT pasa invertido a su salida como un “0”, manteniéndose por lo tanto el segundo NOT sin cambio en su condición lógica. Por su parte, el “0” que estaba puesto a la entrada del tercer NOT pasa invertido a su salida como un “1”, con lo cual el segundo NOT deja de estar en una condición lógicamente anómala. Pero el “1” que está ahora a la salida del tercer NOT es puesto de inmediato a la entrada del primer NOT, el cual tiene con esto un “1” tanto en su entrada como en su salida. Esto pone ahora al primer NOT en una condición lógicamente anómala:

Al finalizar el tiempo t3 y comenzar el tiempo t4, transcurrido un tiempo T, el “1” puesto a la entrada del primer NOT pasa invertido a su salida como un “0”. Por otro lado, el “0” puesto a la entrada del tercer NOT pasa invertido a su salida como un “1”, manteniéndose por lo tanto el tercer NOT sin cambio alguno en su condición lógica. Este “1” a la salida del tercer NOT está puesto en la entrada del primer NOT, con lo cual el primer NOT deja de estar en una condición lógicamente anómala al tener una entrada de "1" y una salida de "0". Pero el “1” que estaba puesto a la entrada del segundo NOT pasa ahora a su salida como “0”. Al tener una salida de “0” y al tener como entrada el “0” que le está poniendo el primer NOT, el segundo NOT entra ahora en una condición lógicamente anómala:

Si repetimos el análisis considerando que por los retardos de propagación siempre podemos tener temporalmente alguno de los NOTs con un “1” en la entrada y un “1” en la salida, o bien con un “0” en la entrada y un “0” en la salida, una condición lógicamente anómala que está siendo transferida de un NOT a otro sin parar, llegaremos a la conclusión de que el circuito está oscilando:

Y esta es una oscilación errática que está completamente fuera de nuestro control por estar oscilando el sistema en los linderos de condiciones lógicamente incompatibles. Si queremos ejercer algún tipo de control sobre las oscilaciones que se están produciendo, utilizaríamos un AND como medio de control:

Aquí cuando la entrada en la terminal “gatillo” del AND es “0”, la salida será siempre “0” independientemente del valor lógico que tenga la otra terminal a su entrada. Esto pone un “0” a la entrada del primer AND, el cual después de un tiempo T pasa invertido como un “1” a su salida, y el cuala su vez después de otro tiempo T pasa invertido como un “0” a la salida del segundo NOT que a su vez después de otro tiempo T pasa invertido como un “1” a la salida del tercer NOT, que queda detenido allí por la acción del AND. La configuración se convierte en una configuración estable. Pero al poner un “1” en la terminal “gatillo” del AND el “1” producido con esto a la salida del AND es puesto de inmediato a la entrada del primer NOT, el cual con el “1” que tenía ya a su salida y con el “1” que le está siendo puesto a su entrada entra en una condición lógicamente anómala, iniciándose así la inestabilidad del sistema.

Curiosamente, si en lugar de haber utilizado tres NOTs conectados en serie retroalimentando la salida del último hacia la entrada del primero, hubiéramos utilizado únicamente dos NOTs, entonces no habríamos tenido oscilación alguna, porque un circuito de este tipo puede poseer dos estados estables que son los siguientes:

Y precisamente por poseer dos estados estables, ninguno de los cuales conduce a una condición lógicamente anómala, este circuito es un circuito biestable (desafortunadamente, su utilidad está limitada por el hecho de carecer de entrada alguna, el estado estable que tome al encender la máquina será totalmente impredecible). Y si conectamos cuatro NOTs en serie, también tendremos dos estados estables. En general, si conectamos un número par de NOTs en serie retroalimentando la salida del último hacia la entrada del primero, siempre tendremos un circuito con dos estados estables. Y si conectamos un número impar de NOTs retroalimentando la salida del último hacia la entrada del primero, tendremos un circuito que estallará en oscilaciones fuera de nuestro control.

El circuito oscilatorio construído a base de tres NOTs es demasiado obvio como para no despertar sospechas dentro de un diseño. En circuitos lógicos sencillos como los que se acaban de mostrar, con un poco de práctica es posible descubrir la posibilidad de que se pueda producir alguna carrera que ocasione un pulso o una serie incontrolable de pulsos no-deseados. Pero en la práctica un sistema digital puede estar formado con cientos o quizá miles de componentes lógicos, lo cual vuelve extremadamente difícil el tratar de descubrir tales condiciones de riesgo inesperado por mera inspección visual del circuito. Inclusive el circuito sencillo que acabamos de ver podría aparecer “disfrazado” en una configuración en la cual en lugar el segundo NOT y el tercer NOT son reemplazados con bloques NOR alimentando a su vez otros componentes lógicos. Si la entrada en las demás terminales de entrada de los NORs se vuelve “0” entonces el esquema se reduce a lo que tenemos arriba, y el sistema estallará en oscilaciones incontrolables no previstas por el diseñista, con un problema sumamente difícil de diagnosticar.

Estas condiciones de riesgo pueden ser minimizadas o eliminadas por completo cuando el comportamiento del sistema está bajo el control de algún reloj maestro, alguna “señal de reloj” (clock) que proporcione un lapso de tiempo suficiente entre una transición de señales binarias distintas para permitir que las cosas se estabilicen, esperando a que estos pulsos que a fin de cuentas son temporales hayan desaparecido. Esta es una de las razones para evolucionar el diseño de los circuitos lógicos hacia una lógica cronometrizada en la cual el flip-flop J-K que será estudiado en un capítulo posterior desempeñará un papel importante. En la práctica, se pueden descubrir este tipo de problemas potenciales en un circuito lógico reproduciendo el circuito en un simulador, un programa de computadora en el que no sólo se aplique a la entrada del circuito todas las combinaciones posibles de “unos” y “ceros” sino que también se introduzca un retardo de tiempo (tomado directamente de las especificaciones técnicas de los componentes utilizados) en cada componente. Los diagramas de tiempo simulados de las salidas lógicas de los circuitos indicarán de inmediato la presencia de estos pulsos que normalmente podrían ser difíciles de predecir y detectar.

PROBLEMA: Cuando un flip-flop R-S es "ajustado" (con la terminal "Set" S) o "reajustado" (con la terminal "Reset" R) el cambio se propaga a las salidas Q y Q del flip-flop dilatado únicamente por los retardos de propagación de los bloques NOR o NAND con los que fue contruído. El problema anterior sugiere la necesidad de ejercer algún control sobre estos cambios para evitar la posibilidad de que en un diseño complicado por efecto de alguna retroalimentación el sistema pueda estallar en oscilaciones inesperadas o ciclar en cambios no anticipados. Para garantizar que el flip-flop R-S (o los flip-flops R-S) cambien su estado en sincronía con otras partes del circuito en donde están siendo utilizados, un buen diseño no les permite cambiar de estado a menos de que hayan recibido una autorización de una señal de "reloj". Bajo esta filosofía, a las terminales R y S no se les permite cambiar la salida Q del flip-flop a menos de que una señal aplicada en una terminal C o CLK llamada "reloj" (clock) tenga un valor "alto" (un valor de "1"). Diseñar un flip-flop R-S que pueda satisfacer estos requerimientos.

Controlar de algún modo lo que entra o lo que sale de cualquier componente o circuito lógico requiere a su nivel más básico el uso de compuertas que bajo el control de una señal lógica de "0" ó "1" detengan o permitan el paso de la información. Esto lo podemos lograr con compuertas formadas con bloques AND, y sería el paso obvio para mejorar el diseño básico de un flip-flop R-S. Si tomamos como punto de partida un flip-flop construído con bloques NAND, podemos agregar una compuerta utilizando también bloques NAND (en vez de usar bloques AND), lo cual tiene la ventaja de que podemos utilizar un bloque que es natural en la microelectrónica de los circuitos integrados. El diseño mejorado será como el que se muestra a continuación:

La forma en la cual trabaja este circuito se puede describir mejor con un diagrama de tiempos como el siguiente:

La explicación de este diagrama de tiempos es la siguiente:

Empezamos suponiendo que ambas entradas S y R al flip-flop están en “0”, y que la salida del mismo también es Q=0. Al subir la entrada S de “0” a “1”, normalmente el flip-flop debería entrar en el estado Q=1; pero no lo hace porque no ha recibido autorización de la señal de “reloj” C (el símbolo C viene precisamente de la palabra inglesa clock) para ello. Manteniéndose las entradas en S=1 y R=0, al subir la entrada en la terminal C de “0” a “1” el flip-flop cambia de inmediato su estado de Q=0 a Q=1, porque ya recibió autorización para un cambio de estado. Esto es resaltado por la primera línea roja vertical en el diagrama (a la izquierda). Tras esto y antes del arribo del tercer “pulso” en la terminal C la entrada S cae a “0”, reteniendo el flip-flop R-S su valor de Q=1. Al llegar el tercer pulso no ocurre nada porque el flip-flop, en su acción natural, mantiene su estado Q=1. Después de esto, al subir la entrada R de “0” a “1”, normalmente el flip-flop debería “reajustarse” al estado Q=0; pero no lo hace porque no ha recibido autorización de la señal de “reloj” C para ello. Manteniéndose las entradas en S=0 y R=1, al subir la entrada en la terminal C de “0” a “1” el flip-flop cambia de inmediato su estado de Q=1 a Q=0, porque ya recibió autorización para un cambio de estado. Esto es resaltado por la segunda línea roja vertical en el diagrama. Después, y antes de que llegue el quinto “pulso de reloj”, las entradas son cambiadas a S=1 y R=0, pero el flip-flop mantiene su estado sin cambiar porque el "0" en la terminal C se lo impide. Sólo al inicio del quinto pulso de reloj (resaltado por la tercera línea roja vertical en el diagrama) ocurre la autorización, cambiando la salida de inmediato a Q=1. Tras esto, los valores lógicos en las terminales S y R son cambiados primero a S=1 y R=1 y luego a S=0 y R=1, pero no sucede nada porque aún no llega el sexto pulso de reloj. Pero con estos últimos valores, al llegar el sexto pulso de reloj la salida cae de Q=1 a Q=0, resaltado por la cuarta línea roja vertical en el diagrama. Después viene la caída de “1” a “0” en la terminal R, sin efecto alguno en la salida. Y por último, al llegar el séptimo pulso de reloj, dentro del intervalo que dura el pulso en su condición de “1” ocurren dos “picos” que tienen efectos inmediatos en la salida Q del flip-flop, resaltados por la quinta y la sexta líneas rojas verticales en el diagrama.

Aunque este flip-flop R-S con la terminal de entrada C mostrada representa una mejora sobre el diseño original, el problema con este diseño es precisamente la última condición en la cual pese a que la salida Q del flip-flop NO puede cambiar de estado mientras la terminal C no haya dado su autorización para ello, la salida del flip-flop sí puede cambiar de estado varias veces mientras la terminal C permanezca activada, lo cual requiere algún tipo de correctivo por la vía del rediseño.

Se acostumbra simbolizar este tipo de flip-flop encerrándolo dentro de una “caja negra” como la siguiente:

Podemos interactuar con un flip-flop de este tipo mediante el flip-flop R-S interactivo disponible en la siguiente página:

http://www.play-hookey.com/digital/clocked_rs_latch.html

PROBLEMA: Como se vió en el problema anterior, aún con una terminal de "control" C añadida al flip-flop R-S para, queda el problema de que mientras dicha terminal de entrada esté activada la salida Q del flip-flop estará sujeta a cualquier cambio en el intervalo de tiempo que la entrada C permanezca en un estado que permita cambios en las terminales S y R del flip-flop. En pocas palabras, en vez de cambiar una sola vez cuando la terminal de control dá su autorización para ello, el flip-flop puede cambiar de estado varias veces. ¿Se puede mejorar un diseño de este tipo?

Existe una mejora adicional que se puede implementar al diseño, la cual consiste en permitir cambios en el flip-flop R-S no simplemente cuando la señal de “reloj” C esté alta en “1” (o baja, en “0”, según sea el caso) sino únicamente cuando la señal en la terminal de control C está transitando de “0” a “1” ó de “1” a “0” según sea el caso, únicamente durante un instante del ciclo de reloj cuando está ocurriendo la transición entre los niveles lógicos de la señal C. Ciertamente, el tránsito de “0” a “1” o viceversa en la terminal C representa un intervalo de tiempo mucho más corto que la permanencia por un cierto tiempo de dicha terminal en “1” ó en “0”. Esto se llama activación en el flanco (edge triggering). El símbolo y un diagrama de tiempos para un flip-flop R-S que trabaje de este modo será el siguiente (obsérvese que en el símbolo que de otro modo sería idéntico al anterior hemos puesto en la terminal C una cuña que representa una transición de nivel, dando a entender que los cambios autorizados solo podrán ocurrir en el instante en que se dé una transición):

En este caso hemos supuesto que los cambios autorizados ocurrirán durante una transición negativa en la terminal C, cuando va de “1” a “0”. Podemos modificar este comportamiento haciendo que los cambios autorizados ocurran durante una transición positiva en la terminal C , cuando va de “0” a "1", con el simple remedio de poner un inversor NOT en la terminal C. Obsérvese en el diagrama de tiempos que los cambios en la salida Q del flip-flop ocurren únicamente cuando la señal en la terminal C cae de “1” a “0”, una caída tan rápida que no permite que la salida pueda cambiar varias veces cuando se está llevando a cabo la transición.

Además del flip-flop R-S, existen otros elementos de memoria cuyos cambios de estados también son controlados con una entrada de “reloj” C y los cuales también poseen como salidas dos terminales complementarias Q y Q. Y en ellos también es posible encontrar las variantes tanto de activación permisible en cualquier momento al estar en un nivel de “1” o de “0” dependiendo del diseño ó de activación permisible únicamente cuando ocurre una transición de un nivel al otro; la única diferencia en los símbolos convencionales utilizados para distinguirlos es la pequeña cuña puesta dentro de la “caja” cuya ausencia denota que el elemento es activable en cualquier tiempo al estar en cierto nivel:

y cuya presencia indica que el elemento de memoria es activable únicamente cuando ocurre una transición de nivels:

Podemos interactuar con un diseño mejorado del flip-flop R-S que implementa la activación en el flanco con el circuito interactivo ofrecido en la siguiente página:

http://www.play-hookey.com/digital/rs_nand_flip-flop.html

El circuito mostrado en la página citada en realidad es una configuración mejor conocida como la configuración maestro-esclavo (master-slave). Pero esto ya nos lleva a un tema mejor cubierto en el siguiente capítulo en el que se introduce un flip-flop más potente y más versátil que el flip-flop R-S: el flip-flop J-K.