PROBLEMA: Dados los siguientes diagramas de tiempo para el flip-flop J-K, obténganse los diagramas de tiempo a la salida del mismo en las terminales Q y Q a partir de los diagramas de tiempo proporcionados. Supóngase que el flip-flop J-K está inicialmente en el estado Q=0. Supóngase también que los cambios son motivados por las transiciones de "1" a "0" en la terminal C y que en el estado J=1 y K=1 la terminal C no ejerce ninguna acción.

La salida en la terminal Q basada en las características del flip-flop J-K suponiendo que inicialmente Q=0 es como se muestra a continuación:

La explicación del diagrama de tiempos de la salida Q es la siguiente:

Suponiendo que el flip-flop J-K está inicialmente en el estado Q=0, la transición de "0" a "1" en la terminal C no produce efecto alguno, pero la caída subsecuente de "1" a "0" hace que el flip-flop J-K cambie de estado, pasando de Q=0 a Q=1. La siguiente transición negativa de "1" a "0" en la terminal C hace que la salida Q vuelva a cambiar de estado, pasando de Q=1 a Q=0. Tras esto, aparecen unos "pulsos" en las terminales J y K, pero estos no tienen efecto alguno al permanecer la terminal C en un nivel estático. Tras ascender nuevamente la terminal C de "0" a "1", hay un cambio en el valor de entrada en la terminal J, que es puesta a J=1. Esto prepara al flip-flop para que cuando haya una transición negativa de "1" a "0" en la terminal C el flip-flop J-K pase al estado Q=1 al tener J=1 y K=0 en sus terminales de entrada, que es precisamente lo que ocurre al final del tercer "pulso" en la terminal C. Tras esto, después de que la entrada en la terminal J cae de "1" a "0" sin producir cambio alguno puesto que los cambios los produce únicamente la terminal C, la terminal C sube de "0" a "1" sin producir todavía cambio alguno en la salida, y permanece en "1" mientras el valor en la terminal K sube de "0" a "1". Esto prepara al flip-flop para que cuando haya una transición negativa de "1" a "0" en la terminal C el flip-flop J-K pase al estado Q=0 al tener J=0 y K=1 en sus terminales de entrada, que es precisamente lo que ocurre al final del cuarto "pulso" en la terminal C. Tras esto, la entrada J es elevada de "0" a "1", con lo cual ambas entradas J y K tienen el valor de "1", lo cual tiene como consecuencia directa que cuando ocurran los siguientes dos "pulsos" en la señal de "reloj" C el flip-flop J-K no cambie de estado.

Puesto que la salida en la terminal Q es simplemente el complemento (inverso lógico) de la salida en la terminal Q, el aspecto del diagrama de tiempos mostrado por esta terminal será el siguiente:

PROBLEMA: Demostrar que la salida de un flip-flop J-K, después de que ha ocurrido una transición, está dada por:

Qn+1 = JQn + K·Qn

en donde Qn es la salida del flip-flop J-K antes de llevarse a cabo la transición.

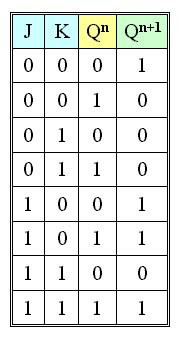

Tomando en cuenta las propiedades del flip-flop J-K, se puede desarrollar la siguiente Tabla de Verdad:

De la Tabla de Verdad se puede obtener ahora Qn+1 en función de J, K y Qn por medio de minterms:

Qn+1 = J·K·Qn + J·K·Qn + J·K·Qn + JKQn

Qn+1 = (J + J)·K·Qn + (K + K)JQn

Qn+1 = JQn + K·Qn

PROBLEMA: Diseñar un flip-flop J-K usando funciones lógicas básicas, utilizando para ello bloques NOR.Qn+1 = (J + J)·K·Qn + (K + K)JQn

Qn+1 = JQn + K·Qn

Para facilitar la comprensión del diseño, se reproducen primero el diagrama esquemático y la Tabla de Verdad del flip-flop R-S hecho con bloques NOR:

Es necesario diseñar primero una configuración en la cual la información a la entrada sea transferida a la salida únicamente cuando la terminal de "reloj" C vaya del estado "1" al estado "0", justo cuando ocurre la transición. Esto presupone necesariamente dos pasos, a saber:

(A) Cuando la terminal C va de "0" a "1".- La configuración es "preparada" para el cambio que habrá de ocurrir. Se almacena dentro de la configuración interna del elemento la información que está puesta a la entrada del mismo.

(B) Cuando la terminal C va de "1" a "0".- La salida de la configuración adquiere el estado a su entrada que fue almacenado por la misma durante la transición de "0" a "1". Esto sugiere el uso de dos flip-flops R-S para construír la configuración.

Para poder implementar lo anterior, se requiere un circuito con dos flip-flops R-S en una configuración maestro-esclavo (master-slave) como se muestra a continuación:

El tipo de compuerta usado debe permitir el flujo de información al ser activada con un "1" y detener todo flujo de información al ser desactivada con un "0". Al ser desactivada con un "0", su salida en sus dos terminales debe ser "0" para que el flip-flop R-S que le sigue retenga al información que se deseaba almacenar (o sea, viendo la Tabla de Verdad del flip-flop R-S hecho con bloques NOR, se requiere que R=0 y S=0 para que el flip-flop retena su estado anterior). Este tipo de compuerta ya lo hemos visto previamente. Se puede construír fácilmente usando funciones AND como se muestra a continuación:

Al ir la terminal C de "0" a "1", la compuerta de entrada permite que se almacene en el flip-flop maestro la información a la entrada de la configuración, a la vez que la compuerta de transferencia entre los dos flip-flops impide que esta información altere la información que está puesta a la salida de la configuración, porque se requiere que la salida permanezca inalterada en la transición positiva de la señal de "reloj".

Al ir la terminal C de "1" a "0", la compuerta de transferencia permite que el flip-flop maestro "imponga" su estado en el flip-flop esclavo, a la vez que la compuerta de entrada detiene todo nuevo flujo de información a la entrada de la configuración, conservando así el flip-flop maestro su estado que está siendo transmitido al flip-flop esclavo.

En el siguiente gráfico animado (ampliar imagen para poder ver la animación en acción) se muestra una configuración "maestro-esclavo" de flip-flops hechos con bloques NAND:

En el extremo superior izquierdo tenemos la simulación de un osciloscopio actuando como analizador lógico que nos permite ver el pulso que está siendo aplicado en la terminal de "reloj" C a la entrada del circuito. Obsérvense las dos acciones que ocurren cuando (a) el pulso de entrada va de "0" a "1", y (b) cuando va de "1" a "0".

Falta ahora relacionar las entradas S0 y R0 del circuito con las terminales J y K externas al circuito que le vamos a agregar y que eventualmente identificaremos como las terminales J y K, tomando en cuenta el estado en el cual se encuentra la salida Q del segundo flip-flop (el flip-flop esclavo) que vendría siendo la salida de todo el circuito.

Cuando J=1 y K=0, si Q=0 entonces después de una transición el circuito quedará en el estado Q=1. Para que esto ocurra en nuestra configuración se requiere que S0=1 y R0=0. Representando esto en una Tabla de Verdad:

Cuando J=1 y K=0, si Q=1 entonces el flip-flop J-K conservará su estado sin que lo afecten las transiciones en la terminal C. En nuestra configuración esto equivale a tener S0=0 y R0=0 para que retenga su estado y sea inmune a las transiciones en la terminal C. Por lo tanto:

Usando razonamientos como los anteriores, encontramos también que:

Cuando J=1 y K=1, el flip-flop J-K retiene su estado anterior (ya sea Q=1 ó Q=0) sin que lo afecten las transiciones en la terminal C. Para lograr el mismo efecto, nuestra configuración requiere S0=0 y R0=0. Por lo tanto:

Cuando J=0 y K=0, el flip-flop J-K cambia de estado después de cada transición. Si J=0, K=0 y Q=0, el flip-flop J-K cambiará al estado Q=1 después de una transición, efecto que obtenemos en nuestro circuito con S0=1 y R0=0. Por lo tanto:

Asimismo, cuando J=0, K=0 y Q=1, el flip-flop J-K cambiará al estado Q=0 después de una transición, lo cual se logra en nuestro circuito con con S0=0 y R0=1. Por lo tanto:

Juntando toda la información anterior en una sola Tabla de Verdad:

Podemos ahora obtener los valores Boleanos que deben tener S0 y R0 en función de los valores que tengan J y K para que nuestra configuración se pueda comportar como un flip-flop J-K. Usando minterms:

S0 = J·K·Q + J·K·Q

S0 = (J + J)K·Q

S0 = K·Q

S0 = K + Q

S0 = (J + J)K·Q

S0 = K·Q

S0 = K + Q

y:

R0 = J·K·Q + JKQ

R0 = JQ(K + K)

R0 = JQ

En esta última línea podemos aplicar "a la inversa" una de las leyes de DeMorgan de la siguiente manera:

para obtener así una expresión final para R0 que se pueda construír mediante un bloque NOR.

Con estas dos relaciones para S0 y R0 implementables con bloques NOR (éste fue a fin de cuentas el objetivo verdadero detrás de las manipulaciones Boleanas mostradas), las cuales llevan a cabo primero la suma Boleana de las entradas y tras esto efectúan el complemento de la suma, podemos ver que el diseño del circuito toma ahora el siguiente aspecto:

PROBLEMA: Con la ayuda de un analizador lógico, un técnico obtiene en la carátula del analizador los siguientes diagramas de tiempo para un flip-flop J-K:

¿Qué tipo de flip-flop J-K es el que describen estos diagramas de tiempo? Explicar en detalle lo que está sucediendo desde el principio hasta el final de los diagramas de tiempo.

Comparando los pulsos de entrada en la terminal de reloj C (clock) con lo que ocurre a la salida Q del flip-flop, es obvio que las transiciones ocurren para este flip-flop cuando la señal de reloj va de "0" a "1" en vez de ocurrir cuando va de "1" a "0". Este flip-flop J-K es por lo tanto uno activado por las transiciones positivas (de "0" a "1") en la terminal de "reloj".

Al principio, la terminal J sube de "0" a "1". Pero como no es esta terminal la que produce las transiciones, no ocurre nada. Tras esto, la señal de "reloj" sube de "0" a "1", y por estar las entradas del flip-flop J-K puestas a J=1 y K=o cuando esto ocurre, el flip-flop que estaba en el estado Q=0 pasa al estado Q=1, mientras que su salida complementaria que estaba en el estado Q=1 pasa al estado Q=0. Una vez que esto ha ocurrido, la entrada J es bajada de "1" a "0" y tras esto la entrada K es subida de "0" a "1", de modo tal que cuando la señal de "reloj" sube de "0" a "1" estando puestas las entradas a J=0 y K=1 en el siguiente ascenso positivo del pulso posterior del "reloj" el estado Q=1 pasa a ser el estado Q=0, mientras que la salida complementaria que estaba en el estado Q=0 pasa al estado Q=1. Posteriormente la señal en la entrada K cae de "1" a "0" y vuelve a subir de "0" a "1", lo cual por sí solo no tiene efecto alguno en el comportamiento del flip-flop, y al ocurrir la tercera transición positiva del pulso de reloj las entradas están a los mismos valores J=0 y K=1 que tenían en la transición anterior, de manera que no se manifiesta cambio alguno. Entre el tercer y el cuarto pulso de reloj hay transiciones en las terminales J y K que no producen cambio alguno, como era de esperarse. En la cuarta transición positiva de la señal de reloj las terminales J y K están ambas al mismo valor de "1", y se produce una transición de Q=1 a Q=0, repitiéndose los cambios que hacen que el flip-flip J-K transite entre estados opuestos con cada transición positiva de la señal de reloj. Esto nos confirma que el flip-flop J-K está construído con bloques NAND.

PROBLEMA: Ilustrar una manera en la cual se pueda poner de modo "forzado" al flip-flop J-K ya sea en el estado Q=0 o en el estado Q=1 sin necesidad de tener que utilizar una terminal C.

Tomando como base el diseño previo de un flip-flop J-K construído con bloques NOR, esto se puede lograr usando flip-flops de tres entradas en lugar de dos en el flip-flop esclavo de la configuración. Dicho elemento tomará el siguiente aspecto:

Estudiando la configuración y tomando en cuenta las propiedades del flip-flop J-K hecho con bloques NOR, encontramos que al activar la terminal Rd de acción "directa" hacia la salida Q con un "1", el flip-flop J-K es forzado a entrar en la condición Q=0. Asimismo, al activar la terminal Sd con un "1" el flip-flop J-K es forzado a entrar en la condición Q=1. Se puede observar que ambas terminales Rd y Sd no deben ser activadas al mismo tiempo, ya que se colocaría al flip-flop esclavo interno (y por lo tanto al flip-flop J-K en un estado no-definido. También podemos observar que mientras una de las terminales permanezca activada, el flip-flop J-K no responderá a los valores que tomen las entradas J, K y C.

Una forma de representar un flip-flop J-K con terminales de "limpieza" R y "preajuste" S directas es como sigue:

Nótese que la cercanía de la terminal S con la salida Q sugiere que al ser activada S el "1" con el cual es activada pasa a la salida más cercana que es en este caso Q. De la misma manera, al ser activada R, el "1" con el cual es activada pasa a Q.

En la literatura técnica es frecuente llamar a las terminales R y S como "clear" y "preclear". Desafortunadamente, al abreviar el símbolo de la terminal de "limpieza" clear con la letra C (de clear) se puede confundir con el símbolo para la terminal de reloj C que para evitar confusiones a veces es redesignada como CLK.

Los circuitos integrados comerciales flip-flops J-K puestos a la venta generalmente tienen incluídas estas terminales de "limpieza", y como ejemplo de ello se puede citar el circuito integrado 4027 fabricado con tecnología CMOS:

el cual incluye dos flip-flops J-K (simbolizados en el diagrama como F/F). En el flip-flop 1, el equivalente de nuestra terminal S que forza al flip-flop a entrar en el estado Q=1 está puesto en la terminal 9 del circuito integrado (SET 1), mientras que el equivalente de nuestra terminal R que "limpia" al flip-flop poniéndolo en el estado Q=0 está puesto en la terminal 12 del circuito integrado (RESET 1).

El uso de terminales de "limpieza" en cada circuito de memoria es sumamente útil cuando se enciende un sistema digital que había estado apagado por algún tiempo, ya que durante el proceso de encendido cada uno de los elementos de memoria puede entrar en un estado de "1" ó en un estado de "0" de manera completamente aleatoria, lo cual podría ser reinterpretado erróneamente por el sistema al empezar a funcionar. La "limpieza" de todos los registros de memoria garantiza de que no habrá nada en los registros que pueda ser malinterpretado durante el procedimiento de arranque. Este proceso de "limpieza" es precisamente lo que se lleva a cabo cada vez que se enciende una computadora de escritorio o que se oprime el botón de RESET (en las que lo tienen) para volver a comenzar de nuevo desde cero, literalmente, en todos los registros de memoria.

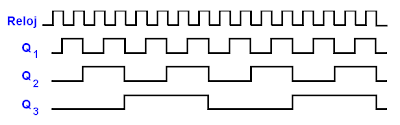

PROBLEMA: La siguiente configuración de flip-flops J-K recibe un tren simétrico de pulsos en la terminal de entrada C del primer flip-flop J-K. Suponiendo que los flip-flops están inicialmente en el estado Q1Q2Q3=000, constrúyase un diagrama de tiempos y a partir del mismo constrúyase una tabla de secuencias en el orden Q3Q2Q1.

¿Qué conclusiones se puede sacar de los resultados obtenidos?

Por tener "ceros" en sus dos entradas J y K, con un tren simétrico de pulsos en la entrada C el primer flip-flop cambiará de estado de Q1=0 a Q1=1 y otra vez de Q1=1 a Q1=0 cada vez que la entrada caiga de "1" a "0". Puesto que la salida de Q1 es a su vez la entrada en la terminal C del segundo flip-flop, el cual también tiene en sus dos entradas J=0 y K=0, este cambiará de estado de Q2=0 a Q2=1 y otra vez de Q2=1 a Q2=0 cada vez que la salida de Q1 caiga de "1" a "0". Y una situación similar aplica al tercer flip-flop. Así pues, el diagrama de tiempos para un tren simétrico de pulsos en la terminal de entrada C empezando con el estado Q1Q2Q3=000 hasta regresar al mismo estado será como se muestra a continuación:

Tomando en cuenta este diagrama de tiempos, la tabla de secuencias correspondiente es la que se muestra a continuación:

Podemos observar de la tabla de secuencias que la configuración presentada es básicamente un contador binario. Tenemos así un circuito lógico que va contando hacia arriba en el sistema de la numeración binaria, la cual fue introducida en el primer capítulo de este libro. Es de esperarse, por lo tanto, que esta configuración tenga aplicaciones importantes en muchos sistemas digitales (y así es, en efecto). Nótese que con tres flip-flops J-K se puede contar en sistema binario en una palabra de tres bits. Por regla general, se puede contar en sistema binario en una palabra de n bits con n flip-flops J-K.

PROBLEMA: La siguiente configuración de flip-flops J-K recibe un tren simétrico de pulsos en la terminal de entrada C del primer flip-flop J-K. Suponiendo que los flip-flops están inicialmente en el estado Q1Q2Q3=111, constrúyase un diagrama de tiempos y a partir del mismo constrúyase una tabla de secuencias en el orden Q3Q2Q1.

¿Qué conclusiones se pueden sacar de los resultados obtenidos?

Este problema es muy parecido al problema anterior. Por tener "ceros" en sus dos entradas J y K, con un tren simétrico de pulsos en la entrada C el primer flip-flop cambiará de estado de Q1=0 a Q1=1 y otra vez de Q1=1 a Q1=0 cada vez que la entrada caiga de "1" a "0". Sin embargo, es la salida complementaria Q1' del primer flip-flop la que está alimentando la entrada C del segundo flip-flop. Por esta razón, el segundo flip-flop cambiará de estado de Q2=0 a Q2=1 y otra vez de Q2=1 a Q2=0 cada vez que la salida de Q1 caiga de "1" a "0". Y una situación similar aplica al tercer flip-flop. Así pues, el diagrama de tiempos para un tren simétrico de pulsos en la terminal de entrada C empezando con el estado Q1Q2Q3=111 hasta regresar al mismo estado será como se muestra a continuación:

Tomando en cuenta este diagrama de tiempos, la tabla de secuencias correspondiente es la que se muestra a continuación:

PROBLEMA: El Registro de Transferencia. Analizar la siguiente configuración suponiendo que ésta recibe un tren simétrico de pulsos en la terminal de entrada. Supóngase que las entradas J y K del primer flip-flop mantienen un valor constante de "0" y "1" respectivamente. Supóngase también que el circuito está inicialmente en el estado Q1Q2Q3Q4=1011. Constrúyase una tabla de secuencias para la sucesión de eventos.

Siendo la condición inicial Q1Q2Q3Q4=1011, se tiene al comenzar la siguiente situación:

Antes que nada, notamos que las entradas en las terminales J y K de cada flip-flop son complementarias entre sí. En esta circunstancia, Q tomará el valor de J después de una transición de "1" a "0" en cada flip-flop. En la primera transición, el flip-flop 4 toma el valor Q3 a la salida del flip-flop 3, produciendo Q4=1, el flip-flop 3 toma el valor del flip-flop 2 produciendo Q3=0, el flip-flop 2 toma el valor del flip-flop 1 produciendo Q2=1 y el flip-flop 1 toma el valor de "0" que está puesto en su entrada J produciendo Q1=0. Esta cadena de eventos es posible debido a que hay un retardo de tiempo dentro de cada flip-flop que después de la transición "retarda" la información el tiempo suficiente para que la información a su salida pueda ser leída por el flip-flop que le sigue.

Pictóricamente, esto se puede representar de la siguiente manera imaginando el recorrido de la información a través de cada flip-flop (inmediatamente después del comienzo de una transición) como área sombreada de color amarillo:

Podemos ver en forma rudimentaria con el mecanismo arriba mostrado cómo es posible que un flip-flop "lea" información de otro flip-flop que le precede reteniendo al mismo tiempo la información a su salida el tiempo suficiente para que el siguiente flip-flop la pueda leer. Visto esto, podemos continuar con el análisis para observar lo que ocurre después de cada transición.

Primera transición:

La condición es Q1Q2Q3Q4=0101.

Segunda transición:

La condición es Q1Q2Q3Q4=0010.

Tercera transición:

La condición es Q1Q2Q3Q4=0001.

Cuarta transición:

La condición es Q1Q2Q3Q4=0000.

La quinta transición y las transiciones subsecuentes no lograrán sacar al circuito del estado Q1Q2Q3Q4=0000, de manera que en este punto detenemos el análisis.

La tabla de secuencias para cada transición sucesiva empezando con la condición Q1Q2Q3Q4=1011 será, basada en los resultados obtenidos, como se muestra a continuación:

Podemos ver que después de cada transición, la palabra almacenada originalmente es desplazada un bit hacia la derecha, siendo enviada al mundo exterior por el último flip-flop (el flip-flop 4). Circuitos de este tipo reciben el nombre de registro de transferencia (ó registro de desplazamiento, ó registro de corrimiento y tienen aplicaciones importantes en los circuitos lógicos. En este caso, el registro de transferencia (shift register) fué usado para leer una palabra almacenada en forma serial (esto es, bit por bit). El registro de transferencia también puede ser usado para escribir en el mismo una palabra introduciéndola bit por bit en el primer flip-flop (el flip-flop 1) para su uso subsecuente.

PROBLEMA: Ilustrar la manera en la cual se puede evitar perder la información contenida en un registro de transferencia al ir sacando la información del registro en forma serial. Construír una tabla de secuencias para mostrar la acción del circuito, usando la palabra 10110 como base.

La forma en la cual se puede evitar perder la información que va saliendo fuera es conectando la salida del circuito (el Registro de Transferencia) que provee la información a la entrada del mismo. Bajo este esquema, la terminal Q del último flip-flop J-K es conectada a la terminal J del primer flip-flop, y la terminal Q del último flip-flop es conectada a la terminal K del primer flip-flop. La idea esencial es la siguiente:

De esta manera, después de la primera transición, el último bit que estaba a la salida del registro es almacenado a la entrada en el primer flip-flop, cuyo lugar estaba vacante por haberse recorrido la palabra de n bits un bit a la derecha. En las transiciones subsecuentes, los bits a la salida van "rellenando" los lugares vacantes que va dejando la palabra al irse recorriendo a la derecha bit por bit. Después de n transiciones, la palabra habrá sido "recuperada" por el Registro y, además, ha sido proporcionada como información bit por bit en forma serial al mundo exterior.

Este tipo de registros se conoce comunmente como registro recirculante.

Un registro recirculante con capacidad de almacenamiento de 3 bits se muestra a continuación:

Una tabla de secuencias para la acción de este tipo de circuito empezando con la palabra 10110 será como la que se muestra a continuación:

PROBLEMA: Explicar en detalle el diagrama de tiempos mostrado para el siguiente registro de desplazamiento. (La imagen tiene acción animada para ayudar a captar mejor lo que está sucediendo, siendo necesario llevar a cabo el procedimiento de ampliar imagen para poder ver la animación.)

La explicación se dará tomando como punto de referencia los tiempos numerados del 1 al 11 puestos encima del diagrama de tiempos.

Al comienzo del tiempo 1, la única señal de entrada a cada uno de los flip-flops J-K mostrados es un "1" puesto mediante la terminal "Reset" del circuito a través del alambre rojo. Puesto que la entrada de este "1" en cada flip-flop es complementada como R, entonces lo que viene entrando a fin de cuentas es un "0" como señal de "Reset", el cual no tiene efecto alguno en ninguno de los cuatro flip-flops.

Al comienzo del tiempo 2, se aplica un "1" en la terminal "Set" del circuito y se aplica también un "1" en la terminal S1 a la entrada del primer NAND, cuya salida va conectada al primer flip-flop (en el extremo izquierdo del circuito). Los dos "1" puestos a la entrada del NAND son convertidos a un "0" a la salida del mismo, el cual al ser complementado como S en el primer flip-flop le viene poniendo un "1" en su terminal de "Set". Esto forza la salida Q1 del primer flip-flop a tomar el valor de "1". Los tres flip-flops restantes no experimentan cambio alguno por tener cada una de las terminales S2, S1 y S4 un "0", lo cual produce un "1" a la salida de cada uno de los NANDs restantes que se convierte en un "0" en las entradas complementadas S de los flip-flops restantes.

Al terminar el tiempo 2 y comenzar el tiempo 3, las señales de "1" son removidas de las terminales "Set" y S1 del circuito, a la vez que se aplica el inicio de un pulso de reloj en la terminal "Shift", el cual aún no tendrá efecto alguno puesto que los cambios ocurren en las transiciones de la señal de reloj de "1" a "0" y no cuando va de "0" a "1".

Al terminar el tiempo 3 y comenzar el tiempo 4, bajo la acción de la caída de "1" a "0" del pulso de reloj aplicado en la terminal "Shift" la salida Q1 del primer flip-flop pasa a la entrada J del siguiente flip-flop a su derecha poniéndolo en el estado Q2=1, mientras que el primer flip-flop entra en el estado Q1=0 al estar siendo alimentado en su terminal J con el "0" que está poniendo el último flip-flop en su salida Q4. Los dos flip-flops intermedios permanecen con salidas de "0".

Al terminar el tiempo 4 y empezar el tiempo 5 se aplica nuevamente en la terminal "Shift" el inicio de otro pulso de reloj, aunque de nueva cuenta no ocurre nada puesto que se supone que para todos estos flip-flops los cambios ocurren en las transiciones de la señal de reloj de "1" a "0".

Al terminar el tiempo 5 y comenzar el tiempo 6, con la caída del pulso de reloj de "1" a "0" la salida del segundo flip-flop pasa al siguiente flip-flop a su derecha poniéndolo en el estado Q3=1, mientras que los flip-flops precedentes entran en los estados Q1=0 y Q2=0. El flip-flip con salida Q4 también permanece en el estado "0".

Al terminar el tiempo 6 y comenzar el tiempo 7, se aplica en la terminal "Shift" el inicio del siguiente pulso de reloj, pero no ocurre nada puesto que los cambios en los flip-flops ocurren en las transiciones de la señal de reloj de "1" a "0".

Al terminar el tiempo 7 y comenzar el tiempo 8, con la caída del pulso de reloj de "1" a "0" la salida de Q3=1 del tercer flip-flop pasa al cuarto flip-flop, a su derecha, poniéndolo en el estado Q4=1, mientras que todos los flip-flops precedentes entran en los estados Q1=0, Q2=0 y Q3=0.

Al terminar el tiempo 8 y comenzar el tiempo 9, la aplicación simultánea de un "1" en la terminal "Set" del circuito y de un "1" en las terminales S1, S2, S3 y S4 tiene el efecto de forzar a todos los flip-flops J-K a entrar en los estados Q1=1, Q2=1, Q3=1 y Q4=1 por las razones señaladas al principio.

Al terminar el tiempo 9 y comenzar el tiempo 10, aunque los "1" puestos en las terminales de "Set", S1, S2, S3 y S4 son removidos, los flip-flops permanecerán en sus estados con salidas de "0", puesto que este es precisamente el objetivo de una señal de "Set" o "Ajuste" a "1". Y permanecerán en dichos estados hasta el inicio del tiempo 11.

Por último, al comenzar el tiempo 11, la terminal "Reset" de todo el circuito cae de "1" a "0". Puesto que este "0" entra a cada flip-flop J-K complementado como R, entonces lo que viene entrando a fin de cuentas es un "1" como señal de "Reset", lo cual tiene el efecto de forzar a todos los flip-flops J-K a entrar en los estados Q1=0, Q2=0, Q3=0 y Q4=0.

Esto concluye el análisis del diagrama de tiempos mostrado.

PROBLEMA: Analizar el circuito que se muestra a continuación. (Sugerencia: Supóngase que el circuito está inicialmente en el estado Q1Q2Q3=000, y constrúyase una tabla de secuencias para el mismo.)

Este circuito es muy similar a un "registro recirculante", con la diferencia de que las salidas del último flip-flop (en este caso, el flip-flop 3) están invertidas antes de ser conectadas a las entradas del flip-flop al principio de la configuración (el flip-flop 1). La salida Q del tercer flip-flop está conectada a la entrada K del primer flip-flop y la salida Q del tercer flip-flop está conectada a la entrada J del primer flip-flop. Suponiendo que el estado inicial es Q1Q2Q3=000, podemos construír una tabla de secuencias siguiendo la secuencia propiciada por una alimentación de pulsos de "reloj" en la terminal de entrada, tomando a la vez en cuenta el comportamiento de los flip-flops J-K en este tipo de circuito:

Este circuito recibe los nombres de contador de anillo caminante (walking ring counter), contador Johnson (Johnson counter), contador de anillo complementario (complementary ring counter) y anillo de código Grey (Grey code ring), entre otros tantos.

PROBLEMA: El flip-flop D. Los problemas anteriores indican que la mayoría de los circuitos lógicos centrados en la configuración del tipo "registro de transferencia" siempre usan terminales complementarias a la entrada en las terminales J y K de cada flip-flop usado. Considerando esto, ¿qué simplificación se puede hacer con los bloques fundamentales del sistema?

Tomando en cuenta que en este tipo de circuitos se desea que la salida Q de cada flip-flop tome directamente el valor de su entrada J después de cada transición de "1" a "0" en la terminal de "reloj" C, y que para que esto ocurra es indispensable que la alimentación a la terminal K sea el complemento del valor lógico en la terminal J, podemos hacer la siguiente mejora al flip-flop J-K:

Esta configuración se simplifica generalmente encerrándola en una "caja negra" con la siguiente simbología, reteniendo todas sus características originales:

Este bloque representa el elemento conocido comunmente como el flip-flop D; y aunque menos versátil que el flip-flop J-K, requiere de mucho menos conexiones que el flip-flop J-K en una infinidad de circuitos, o sea, ofrece menos problemas de alambrado en la construcción de circuitos lógicos. El flip-flop D es tan útil y tan versátil que se puede adquirir en pares dentro de un circuito integrado de bajo costo como el 4013 (construído con tecnología CMOS, véase el Suplemento # 1: Las familias lógicas):

Las terminales de Set S y de Reset R son para "forzar" a cada flip-flop D a entrar en el estado Q=1 y en el estado Q=0, respectivamente, independientemente del estado en el que se haya encontrado previamente. Un aspecto interesante de la tecnología CMOS usada por este circuito integrado es que el voltaje VDD de la fuente de poder puede variar desde +3 volts hasta +15 volts, como lo indica el diagrama, y aún así el circuito integrado será capaz de interpretar la presencia o ausencia del mismo como un "1" ó como un "0".

Además del circuito integrado mencionado, tenemos otros como el CD40175 (también fabricado con tecnología CMOS) cuya relación de terminales "pins" en el circuito integrado es la siguiente (obsérvese que la señal de "reloj" o clock puesta en la terminal 9 actúa simultáneamente sobre los cuatro flip-flops D que hay dentro del circuito integrado, lo cual es una gran ayuda para diseños en los que es importante mantener a todos los componentes sincronizados):

o como el circuito integrado CD4175 (también fabricado con tecnología CMOS) cuyo diagrama funcional interno es el siguiente:

Además de ser fabricado con tecnología CMOS, el flip-flop D también ha sido fabricado con tecnología TTL, de lo cual se muestra como ejemplo el circuito integrado octal 74LS374 (el prefijo "74" indica que pertenece a la familia TTL de circuitos lógicos, y el sufijo intermedio "LS" significa Low power Schottky señalando que es de consumo bajo de energía y de alta velocidad):

el cual contiene ocho flip-flops D independientes el uno del otro, excepto por el hecho de que, como puede verse en el diagrama para este circuito integrado, todos los flip-flops D están conectados a la misma terminal de "reloj" designada CK, la cual viene de la terminal 11.

PROBLEMA: Diseñar un registro de transferencia con capacidad de 4 bits, del tipo "entrada serial, salida serial", usando flip-flops D.

Con la entrada designada como "In" y la salida como "Out" tal y como se acostumbra en mucha literatura técnica, el circuito pedido tiene la siguiente configuración:

Este tipo de registro también es conocido en la literatura técnica como registro siso (serial-in serial-out).

La simpleza del diseño en este caso usando flip-flops D en lugar de flip-flops J-K es obvia. La cantidad inferior de alambrado requerido se reflejaría en un circuito impreso como una menor cantidad de líneas requeridas en la tablilla para interconectar los elementos.

PROBLEMA: Diseñar un registro de transferencia con capacidad de 3 bits, del tipo entrada-paralela salida-serial, usando flip-flops D.

Tomando en cuenta que en la entrada paralela se introducen todos los bits de información al mismo tiempo, el diseño en cuestión será como sigue:

La forma en la cual trabaja este circuito es la siguiente: la palabra binaria de entrada de tres bits es colocada en las terminales de entrada Bin(1), Bin(2) y Bin(3). Tras esto, se tiene que activar la terminal que dá la autorización para escribir la palabra dentro del registro, la terminal de escritura W (Write), la cual activa tres bloques AND que sirven como compuertas. Una vez que la terminal W es activada con un "1", se aplica un pulso de reloj con el cual cada uno de los flip-flops D es "cargado" con su bit correspondiente. Hecho esto, se remueve el "1" de la terminal W, con lo cual no entrará información alguna de los AND hacia los flip-flops. Y puesto que la salida Q de cada flip-flop está conectada a la entrada D del que le sigue excepto el tercero por el cual irá saliendo la información en la terminal de salida Out, la aplicación de pulsos sucesivos en la terminal de "reloj" hará que la información avance en forma serial de un flip-flop al siguiente. Este mismo principio de diseño se puede extender hacia un registro de este tipo con cualquier cantidad de flip-flops.

Este tipo de configuración es esencialmente útil en lugares en donde el procesamiento de información se lleva a cabo en forma paralela, manejando varios bits al mismo tiempo en una sola operación. El procesamiento de información en forma paralela es, por regla general, más rápido que el procesamiento de informaciónen forma serial, aunque algo más costoso por el número de componentes adicionales y líneas de conducción eléctrica adicionales que se requieren, según se puede ver comparando la estructura del circuito en este problema con la estructura del circuito del problema anterior.

Un circuito de esta naturaleza es tan útil, que inclusive es puesto a la venta en circuitos integrados comerciales como el CD4014:

fabricado con tecnología CMOS que contiene un registro de transferencia de ocho bits este tipo. Este circuito integrado puede ser utilizado como un registro de transferencia de 6, 7 u 9 etapas, ya sea como un registro de transferencia de entrada serial salida serial, o como uno de entrada paralela salida serial, y se puede conectar en "cascada" para obtener longitudes mayores. Para utilizarlo como un registro de transferencia del tipo entrada paralela salida serial, activamos la terminal "pin" 9 (Par/Ser) con un "1", mientras que para utilizarlo como un registro de transferencia del tipo entrada serial salida serial aterrizamos la misma terminal con un "0". Es importante tomar nota de que en esta misma terminal usada para seleccionar dos modos diferentes de operación, la opción de operación Par se activa poniéndole un "1" a la terminal, mientras que la opción de operación Ser que está complementada se activa poniéndole un "0" a la misma terminal. Esta notación técnica es de uso general. Los datos que van siendo metidos en forma serial por la terminal 11 de entrada (Serial Input) son transferidos por la primera etapa en cada transición positiva (de "0" a "1") de la señal de "reloj" aplicada en la terminal 10 (Clock Pulse). Tras seis pulsos sucesivos de reloj, estos datos comienzan a aparecer en la terminal 2 identificada como "Q6 Output". Un pulso adicional de reloj transfiere los datos para que el último bit llegue a la terminal 12 identificada como "Q7 Output", y otro pulso adicional hace que este último bit aparezca en la terminal 3 identificada como "Q8 Output". Pulsos adicionales de reloj harán que se pierda este bit de información a menos de que los datos sean recirculados o que se conecte la información en "cascada" hacia otro 4014. Para cargar información paralela, se aplica una palabra de ocho bits (un byte) de las terminales Par 1 Input hasta la Par 8 Input, poniendo al bit de Par 1 Input en la cercanía de la entrada al registro y al bit de Par 8 Input en en la cercanía de la salida del mismo. La palabra de entrada paralela es cargada en forma síncrona (todos los ocho bits entran al mismo tiempo) en la transición positiva de la señal de "reloj".

Existe otro tipo de registro de transferencia en el cual la palabra puede ser "cargada" de inmediato sin necesidad de tener que esperar a la aplicación de un pulso de reloj, y ejemplo de ello es el circuito integrado 4021:

también fabricado con tecnología CMOS y también con capacidad de ocho bits.

PROBLEMA: Diseñar un registro de transferencia con capacidad de 3 bits, del tipo entrada-serial salida-paralela, usando flip-flops D.

Este tipo de diseño es extremadamente sencillo. Tomando en cuenta que en la salida paralela se extraen todos los bits de información al mismo tiempo, el diseño en cuestión será como sigue:

En este caso, para introducir una palabra binaria, vamos colocando bit por bit dicha palabra en la terminal de "Entrada", avanzando simultáneamente dicha palabra dentro del registro de transferencia. Una vez introducida en el mismo, la podemos sacar en forma paralela activando la terminal de lectura R (Read). Es importante agregar que los bloques AND que están haciendo la función de una compuerta en realidad son optativos, porque de cualquier manera una vez adentro del registro de transferencia la palabra binaria está disponible para su lectura inmediata.

Un circuito de esta naturaleza es tan útil, que inclusive es puesto a la venta en circuitos integrados comerciales como el CD4015:

fabricado con tecnología CMOS, el cual contiene dos registros de transferencia independientes de 4 bits, e inclusive cada uno de los dos registros tiene su propia terminal de reloj. Otro circuito integrado más reciente de este tipo lo es el CD4094, de ocho bits, también fabricado con tecnología CMOS:

Este tipo de circuitos integrados se pueden conectar en "cascada" para aumentar la capacidad de los mismos. Así se pueden conectar dos circuitos integrados CD4094 de la manera siguiente:

PROBLEMA: Diseñar un contador de "Anillo Caminante" de cuatro bits usando flip-flops D.

Considerando que el contador de "Anillo Caminante" es un registro de transferencia con el complemento de las salidas del último flip-flop alimentando las entradas del primer flip-flop (que es a lo que equivale el "cruzar" las salidas del último flip-flop antes de conectarlas a las entradas del primero), el diseño será como sigue, tomando como base el diseño llevado a cabo en un problema previo con flip-flops J-K:

PROBLEMA: Diseñar un registro recirculante con tres bits de capacidad, del tipo entrada-serial salida-serial, usando flip-flops D.

Un diseño con las características pedidas, capaz de poder dar la "autorización" para ir metiendo una palabra binaria en forma serial dentro del mismo activando la terminal W (Write) y desactivándola cuando la palabra ya está metida y será puesta a "recircular", es el siguiente:

En este caso, para introducir una palabra binaria en el registro recirculante a través de la terminal de entrada In, activamos primero con un "1" la terminal de "escribir" W (Write), metiendo dicha palabra en forma serial bit por bit dentro del circuito con varias transiciones en la terminal de "reloj". Una vez introducida la palabra dentro del registro recirculante, desactivamos la terminal de escritura W con un "0", con lo cual el circuito trabajará como un registro recirculante sin perder la información almacenada.

PROBLEMA: Diseñar un registro de transferencia para almacenar un número decimal en sistema BCD, de rapidez óptima, usando flip-flops D. Diseñar asimismo un registro para una calculadora electrónica con capacidad para seis dígitos.

Considerando que la representación decimal de un número en sistema BCD requiere de cuatro bits para su representación, y que el registro de transferencia más rápido posible es el de entrada-paralela y salida-paralela o pipo (parallel-in parallel-out), el diseño deberá ser como sigue:

Puesto que la calculadora electrónica utiliza el sistema BCD (por lo menos para mostrarle el número al usuario en sistema decimal que pueda entender en lugar del lenguaje de "unos" y "ceros" usado por la máquina), si esta es de seis dígitos deberá poder almacenar seis cifras en sistema BCD, usando cuatro bits para almacenar cada cifra decimal. Esto sugiere que podemos usar el diseño pipo de arriba como bloque fundamental. Tomando en cuenta que en toda calculadora los números van entrando de izquierda a derecha, desplazándose todos los números un espacio a la vez para poder ir entrando en el registro de la calculadora, el registro tomará el siguiente aspecto:

Este tipo de registro recibe en ocasiones el nombre de registro de almacenamiento. En la mayoría de las calculadoras hay varios de este tipo. Uno de ellos es el que mantiene los números decimales que le están siendo mostrados al usuario. Otro de ellos es uno al que simplemente se le conoce como la memoria (de la cual puede haber varias), a la cual tenemos acceso con alguna tecla como "M+" ó "M-".

PROBLEMA: Subrutinas Denegadas. Supóngase que un contador de anillo caminante con capacidad de almacenamiento de 3 bits hecho a base de flip-flops D incurre en la condición Q1Q2Q3=101. ¿Qué ocurre en este contador después de varias transiciones producidas por un tren de pulsos en la terminal de "reloj"?

Analizamos primero lo que ocurre después de varias transiciones empezando con la condición Q1Q2Q3=101 que es la siguiente:

Primera transición:

El estado del contador después de la primera transición es Q1Q2Q3=010.

Segunda transición:

El estado del contador después de la segunda transición es Q1Q2Q3=101.

Tercera transición:

El estado del contador después de la primera transición es Q1Q2Q3=010.

Hasta este punto, el análisis nos ha dado suficiente información.

El contador cambia del estado 101 al estado 010 y viceversa, y no hay forma en la cual se pueda sacar a sí mismo de estos dos estados.

Los dos estados en los que está atorado el contador de anillo caminante son ejemplos de lo que comúnmente se conoce como subrutinas denegadas (disallowed subroutines), las cuales pueden ocasionar innumerables problemas si no se les reconoce a tiempo. Esto que ocurre al nivel de la máquina refleja algo que también puede ocurrir cuando se está elaborando un programa computacional, en donde un "salto incondicional" de una instrucción del programa a otra puede eventualmente después de varios pasos conducir a la misma instrucción que produjo el salto, atorando al programa en un bucle perpetuo del que no podrá salir. Este problema a nivel de la programación de las computadoras fue eliminado en gran parte con la introducción del concepto de la programación estructurada por Edward W. Dijkstra, el cual hizo ver que los saltos incondicionales en un lenguaje de alto nivel no son realmente necesarios, pudiendo por lo tanto ser corregidos por el programador por una buena práctica de programación. Pero ningún programador por bueno que sea puede corregir algo que está sucediendo al nivel de la máquina, dentro de sus circuitos.

Todo estado que pueda conducir a un contador a una subrutina denegada es conocido como un estado denegado (disallowed state).

El contador de anillo caminante puede incurrir en cualquiera de estos dos estados denegados de varias maneras. Esta condición puede empezar cuando inicialmente se le aplica energía al sistema. En este caso, el problema se puede solucionar con un pequeño retardo de tiempo al aplicar energía al sistema, durante el cual se pueden "limpiar los registros". Para esto, cada flip-flop D debe poseer una terminal R (reajuste) que lo ponga en el estado Q=0 al ser activado el circuito. El diagrama adecuado para este flip-flop sería el siguiente:

Con esta modificación, el contador tendrá el siguiente aspecto:

La activación de la terminal para "limpiar" todo poniendo cada uno de los flip-flops en el estado Q=0 pondrá al contador en el estado Q1Q2Q3=000.

Ocasionalmente, se desea tener la opción de poder poner al contador en la condición Q1Q2Q3=111 además de poderlo poner en la condición Q1Q2Q3=000. Para esto, cada flip-flop D utilizado debe poseer, además de la terminal R, una terminal S que lo ponga en el estado Q=1 al ser activada (esto es reminiscente del comportamiento del flip-flop R-S sobre el cual se basan estos flip-flops más sofisticados). El diagrama propio para este tipo de flip-flop sería el siguiente:

Obsérvese que la cercanía de la terminal S a la terminal Q sugiere que al ser activada la terminal S, el "1" pasa directamente a su terminal más cercana que es Q, siendo este el estado que adquiere el flip-flop con la activación de S. La Tabla de Verdad de este último flip-flop D mejorado, para la acción de las terminales R y S deberá ser, basada en las propiedades de R y S aquí indicadas:

En esta tabla de verdad no se toma en cuenta para nada los valores que haya previamente ni en la terminal de entrada D ni en la terminal de salida Q, porque las terminales S y R son absolutas y toman prioridad sobre cualquier otra condición previa en la que haya estado el flip-flop. Obsérvese también que no está permitido activar al mismo tiempo S y R, lo cual conduce a una inconsistencia lógica de propósitos.

Frecuentemente es posible usar los mismos estados en los cuales se puede dar origen a una subrutina denegada para "limpiar los registros" de una manera automática al empezar. Siguiendo esta filosofía, el contador de anillo caminante puede tomar la siguiente configuración:

Con la modificación arriba mostrada, en el caso de que el contador incurra en la condición Q1Q2Q3=010 automáticamente será forzado a entrar en el estado 000.

La técnica de usar los mismos estados denegados para "limpiar los registros" eliminando cualquier posibilidad de ellos se puede aplicar a muchas otras situaciones similares, sobre todo aquellas que puedan considerarse críticas. De cualquier manera, considerando el aumento en la complejidad del circuito, puede ser preferible irse a la limpieza de todo directamente accediendo a todas las terminales R de los flip-flops del circuito al arrancar la máquina con sus operaciones, que es lo que se acostumbra a hacer.

PROBLEMA: Determinar si el contador que se muestra tiene estados denegados.

Analizamos primero la secuencia natural que recorre el contador suponiendo que este está inicialmente en la condición Q1Q2Q3=000. Trabajando sobre el diagrama del circuito, obtenemos cada uno de sus estados después de las transiciones que le son aplicadas a la terminal de "reloj", los cuales resultan ser:

Primera transición: El estado es Q1Q2Q3=100.

Segunda transición: El estado es Q1Q2Q3=110.

Tercera transición: El estado es Q1Q2Q3=011.

Cuarta transición: El estado es Q1Q2Q3=001.

Quinta transición: El estado es Q1Q2Q3=000.

Puesto que en la quinta transición el contador regresa a su estado original, no es necesario proseguir con el análisis.

Para encontrar los posibles estados denegados en el contador, comparamos los estados de su secuencia natural con todos los estados posibles que no están incluídos en la secuencia normal del contador:

Secuencia Natural

Estados Posibles

Vemos entonces que hay tres posibles estados denegados:

Q1Q2Q3=010

Q1Q2Q3=101

Q1Q2Q3=111

Q1Q2Q3=101

Q1Q2Q3=111

Falta ver si el contador se puede "sacar" a sí mismo de cada uno de estos estados. Para esto, hay que analizar el comportamiento del contador empleando cada uno de los tres posibles estados denegados como condición inicial.

Posible estado denegado Q1Q2Q3=010

Condición inicial: Q1Q2Q3=001.

Primera transición: Q1Q2Q3=101.

Segunda transición: Q1Q2Q3=110. (El contador resume su operación normal, ya que este es uno de los estados propios pertenecientes a la secuencia natural del contador.)

Tercera transición: Q1Q2Q3=011.

Posible estado denegado: Q1Q2Q3=101

Condición inicial: Q1Q2Q3=0101.

Primera transición: Q1Q2Q3=110.

Segunda transición: Q1Q2Q3=011. (El contador resume su operación normal, ya que este es uno de los estados propios pertenecientes a la secuencia natural del contador.)

Posible estado denegado Q1Q2Q3=111

Condición inicial: Q1Q2Q3=111.

Primera transición: Q1Q2Q3=011.

Segunda transición: Q1Q2Q3=001. (El contador resume su operación normal, ya que este es uno de los estados propios pertenecientes a la secuencia natural del contador.)

Puesto que el contador puede recuperar su secuencia natural de cualquier estado posible en el que se encuentre, concluímos que el contador no tiene estados denegados.

PROBLEMA: ¿Cuántos estados denegados tiene un contador de anillo caminante de 4 bits, si es que los tiene? ¿Cuántos estados denegados tendrá un contador de anillo caminante de n bits en general, si es que los tiene?

Comparamos primero la secuencia natural del contador de anillo caminante de 4 bits con todos sus estados posibles:

Secuencia Natural

Estados Posibles

Podemos ver que hay ocho posibles estados denegados. Falta comprobar si el contador se puede "sacar" por sí solo de cada uno de estos estados. Empezamos el análisis con el estado Q1Q2Q3Q4=0100. Teniendo en cuenta la forma en la cual trabaja el contador de anillo caminante, obtenemos la siguiente secuencia resultante:

Encontramos que el contador no se puede "sacar" a sí mismo del estado Q1Q2Q3Q4=0100, incurriendo en una subrutina denegada, la cual por cierto contiene todos los estados restantes que faltaban de estudiar.

Concluímos pues que un contador de anillo caminante de cuatro bits contiene ocho estados denegados, o sea, todos los estados restantes posibles que no están incluídos en su secuencia natural de estados.

En general, un contador de anillo caminante de n bits tendrá una secuencia natural de 2n estados, esto de un total de 2n estados posibles. El contador de anillo caminante de n bits tendrá por lo tanto 2n-2n estados denegados.

PROBLEMA: Usando flip-flops D y una memoria ROM, diseñar una máquina secuencial que pueda producir una secuencia de 16 estados diferentes, siendo cada estado un estado de 4 bits.

Como se señaló en el texto principal de este capítulo, existen varias técnicas, algunas de ellas algo sofisticadas, para diseñar circuitos que mediante el empleo de flip-flops J-K y combinaciones de funciones lógicas básicas produzcan ciertas secuencias predeterminadas de números binarios. Pero antes de invertir una cantidad inusual de tiempo tanto en el aprendizaje de dichas técnicas como en la aplicación de las mismas, vale la pena tomar en cuenta otras alternativas apoyadas por el bajo costo de algunos circuitos integrados "estándard". Además de la técnica que ya fue descrita en el texto principal usando una memoria ROM en combinación con un contador binario de conteo ascendente, hay otra técnica que recurre también al empleo de memorias ROM para lograr obtener secuencias de números binarios pero sin necesidad de tener que recurrir a un contador binario ascendente. La idea esencial detrás de esta técnica consiste en que cada dato almacenado bajo cada domicilio se convierta a su vez en el siguiente domicilio de donde el ROM sacará el siguiente dato, lo cual resultará en la secuencia específica de números binarios deseada. La idea esencial está bosquejada en el siguiente diagrama, empleando para ello un ROM con capacidad para almacenar 16 palabras de 4 bits de longitud cada una:

Para que esta idea pueda funcionar, es necesario interponer una compuerta que detenga temporalmente los datos que D0D1D2D3 que están siendo puestos en la entrada de domicilios A0A1A2A3 del ROM, porque de otra manera se establecería una carrera en la cual la palabra binaria puesta en la entrada del ROM sacaría de inmediato el dato especificado por dicho domicilio que sería puesto de inmediato a la entrada del ROM sacando de inmediato el siguiente dato iniciándose así la carrera incontrolable. Esta es precisamente la función de las compuertas: eliminar cualquier posibilidad de carreras incontrolables. Además, queremos controlar la velocidad de nuestra máquina secuencial bajo la acción de "pulsos" de un reloj maestro que traiga a la máquina bajo nuestro control. Esto lo podemos lograr fácilmente usando cuatro flip-flops D conectados para formar un registro de transferencia del tipo entrada-paralela salida paralela:

Para la construcción de este circuito, aquí podríamos utilizar un circuito integrado como el 4035, el cual es precisamente un registro de transferencias de entrada-paralela salida-paralela, adecuado a este propósito.

PROBLEMA: Analizar el comportamiento del flip-flop J-K conectado de la siguiente manera:

Suponiendo que el flip-flop está inicialmente en la condición Q=0, después de la primera transición tomará el estado Q=1. A la segunda transición regresará al estado Q=0 y así sucesivamente.

Este elemento es mejor conocido como el flip-flop T, y su diagrama esquemático es simplificado a la siguiente configuración, con una sola terminal de entrada designada como T (toggle):

En virtud de que este componente carece de entradas, y sólo puede ciclar entre dos estados entre cada pulso de reloj, sus aplicaciones son extremadamente limitadas y se incluye aquí únicamente a manera de información. Un circuito de este tipo, sin la adición de una terminal extra de "limpieza" (clear) que permita ponerlo en un estado fijo anticipable, carece de uso práctico excepto como "divisor de frecuencia" de pulsos rectangulares. Además, pocos diseñistas estarían dispuestos a la adquisición de flip-flops T cuando por prácticamente el mismo precio se pueden adquirir circuitos integrados con la misma cantidad de flip-flops J-K ó flip-flops D que son mucho más versátiles.

PROBLEMA: La siguiente tabla de secuencias dá la impresión de pertenecer a un contador de peso 1-1'-2-5. Confirmar si esto es cierto.

A continuación calculamos el número decimal equivalente producido por este contador según el peso asignado a cada flip-flop J-K:

El contador proporcionado no puede ser un contador con peso 1-1'-2-5, ya que en el orden en el cual ocurren las transiciones estas no dan un total que asciende continuamente de uno en uno. Después de 6 unidades acumuladas el conteo salta hasta 8, regresa a 7 y salta hasta 9, como se ha destacado en números rojos en la última tabla.

PROBLEMA: Construír una tabla de secuencias para un contador con peso 1-1'-3-6.

La especificación proporcionada requiere del uso de cuatro flip-flops J-K, cada uno con salidas Q1, Q1', Q3 y Q6 respectivamente especificadas según el peso que se le va a dar a cada combinación. La tabla de secuencias que requiere un circuito de esta naturaleza es la siguiente:

PROBLEMA: Construír una tabla de secuencias para un contador con peso 1-2-2'-4.

Empezando, como siempre, con el estado "0000", y yendo hacia arriba en conteo ascendente, la tabla de secuencias deberá ser como la que se muestra a continuación:

Puesto que este contador recorre 10 estados diferentes antes de regresar a la condición original Q1Q2Q2'Q4=0000, se puede utilizar como un contador decimal.

PROBLEMA: Encontrar el peso de un contador (o, lo que es lo mismo, determinar los pesos A, B, C y D de los flip-flops con los que está construído) cuya tabla de secuencias es la siguiente:

Podemos determinar el peso de este contador con la ayuda de la siguiente tabla:

La metodología para la construcción de esta tabla es que para la determinación del peso de cada uno de los flip-flops del contador hay que seguir paso a paso cada uno de sus estados, asignándole un peso numérico a cada flip-flop según se vaya requiriendo, con la asignación acumulativa yendo de la izquierda hacia la derecha en la tabla.

Al inicio, con todos los flip-flops en el estado "0", no hay ninguna contribución de ellos al peso numérico del contador, el cual se puede decir que se encuentra en el estado cero.

Cuando el contador ha salido del estado "0000" y ha pasado al estado "1000", como el conteo debe ser siempre ascendente esto significa que tenemos que darle al primer flip-flop un peso numérico de 1, lo cual es puesto en la columna "Conclusión" dándole a A el peso A=1.

Cuando el contador pasa del estado "1000" al estado "0100", si hemos de mantener la cuenta decimal ascendente esto significa que tenemos que darle al segundo flip-flop un peso numérico de 2. Cada vez que se "encienda" el segundo flip-flop con un "1" contribuirá un peso numérico de 2, lo cual es puesto en la columna "Conclusión" dándole a B el peso B=2.

Cuando el contador pasa del estado "0100" al estado "1100", el conteo decimal acumulativo es 3, porque cada uno de los dos primeros flip-flops contribuye con un peso numérico de 1 y de 2, respectivamente, o sea que 1+2=3.

Cuando el contador pasa del estado "1100" al estado "1010", puesto que el número decimal que sigue debe ser 4 y el primer flip-flop ya está contribuyendo con un peso numérico de 1, esto significa que el tercer flip-flop necesariamente debe tener un peso numérico de 3, lo cual es puesto en la columna "Conclusión" dándole a C el peso C=3.

Procediendo de la misma manera, concluímos que el cuarto flip-flop también tiene que tener un peso numérico de 3 al igual que el tercer flip-flip, lo cual es puesto en la columna "Conclusión" dándole a D el peso D=3. Entonces el contador tiene un peso de 1-2-3-3', en donde ponemos la comilla en el cuarto elemento para distinguirlo del tercer elemento que también tiene el mismo peso numérico.

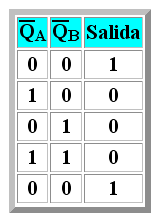

PROBLEMA: El Glitch. Obtener la salida obtenida por la siguiente configuración bajo un tren simétrico de pulsos en la terminal de entrada C. Suponiendo que cada elemento lógico introduce un pequeño retardo de tiempo, ¿qué diferencia habrá entre la salida actual y la salida calculada inicialmente? (Sugerencia: Ignorar el retardo de tiempo introducido por el bloque NOR, el cual es irrelevante para lo que se descubrirá en este problema.)

Puesto que se están usando las salidas QA y QB, es conveniente suponer que la configuración está inicialmente en el estado QAQB=00. Empezando con esta suposición y trabajando sobre el diagrama esquemático del circuito, encontramos que los estados del mismo en las transiciones que se llevan a cabo ocurren en el siguiente orden:

Primera transición: El estado es QAQB=10.

Segunda transición: El estado es QAQB=01.

Tercera transición: El estado es QAQB=11.

Cuarta transición: El estado es QAQB=00.

A la cuarta transición el circuito regresa a su estado original QAQB=00, de modo que no es necesario continuar con el análisis.

El siguiente paso es construír una tabla de secuencias usando la información obtenida:

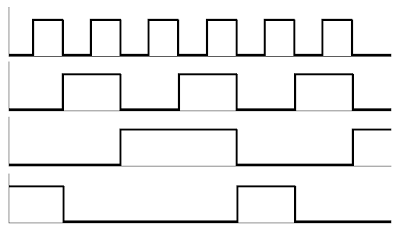

A continuación se muestra el diagrama de tiempos para esta secuencia (el diagrama en el primer renglón corresponde a la entrada de los pulsos de "reloj", el segundo renglón corresponde a la salida QA, el tercer renglón corresponde a la salida QB y el cuarto renglón corresponde a la salida del NOR):

Considerando que cada elemento lógico introduce un pequeño retardo de tiempo (el flip-flop A con respecto a la señal de entrada y el flip-flop B con respecto a la señal que le está siendo puesta por el flip-flop A), el diagrama de tiempos actual será como sigue ignorando el retardo de tiempo introducido por el propio bloque NOR (obsérvese el desfase entre QA y QB y la consecuencia del desfase entre estas señales al entrar al NOR, considerando que cuando ambas entradas a un NOR son "0" la salida del NOR se vuelve "1"):

Comparando la salida actual con la salida esperada idealmente, se puede apreciar la presencia de unos "picos" (encuadrados en línea roja) que no aparecían en el cálculo original. Cada "pico" se conoce como un glitch. Puesto que todos los circuitos lógicos en existencia poseen un retardo de tiempo inherente en su construcción, existen innumerables diseños que irremediablemente producirán glitches. La forma de determinar si un diseño puede producir glitches o no es seguir el método utilizado en este problema, que consiste en obtener el diagrama de tiempos para dicho diseño y luego aplicar los retardos de tiempo señalados en las hojas de las especificaciones técnicas para los elementos usados en el diseño. Cualquier posibilidad de glitch aparecerá inmediatamente de esta manera.

Si un diseño produce glitches, existen varias alternativas para remediar el problema, entre las cuales está utilizar otro tipo de diseño (los circuitos secuenciales síncronos en general tienen menos posibilidades de padecer este tipo de problema que los circuitos secuenciales asíncronos) o introducir retardos de tiempo donde sea necesario para eliminar los glitches. Naturalmente, si todo está bajo el control de un "reloj maestro", siempre es posible usar dicho control para esperar el tiempo suficiente para que los glitches hayan desaparecido al estabilizarse el sistema en cierto estado.

PROBLEMA: Dado el siguiente contador, contestar las preguntas que se dan:

1) ¿Cuál es el módulo del contador?

2) ¿Cuál es el peso del contador?

Empezamos suponiendo que la configuración está inicialmente en el estado Q1Q2Q3Q4=0000. Trabajando sobre el diagrama del circuito, encontramos que los estados después de cada una de las transiciones que cambian al estado del contador son:

Primera transición: El estado es Q1Q2Q3Q4=1000.

Segunda transición: El estado es Q1Q2Q3Q4=0100.

Tercera transición: El estado es Q1Q2Q3Q4=1100.

Cuarta transición: El estado es Q1Q2Q3Q4=0110.

Quinta transición: El estado es Q1Q2Q3Q4=1110.

Sexta transición: El estado es Q1Q2Q3Q4=0101.

Séptima transición: El estado es Q1Q2Q3Q4=1101.

Octava transición: El estado es Q1Q2Q3Q4=0111.

Novena transición: El estado es Q1Q2Q3Q4=1111.

Décima transición: El estado es Q1Q2Q3Q4=0000.

Puesto que el contador recorre diez estados diferentes para regresar a la condición inicial, es un contador módulo-10.

Procedemos ahora a determinar el peso del contador:

Para la determinación del peso, seguimos paso a paso cada estado del contador, asignándole un peso numérico a cada flip-flop según se vaya requiriendo, con la asignación acumulativa yendo de la izquierda hacia la derecha.

Al inicio, con todos los flip-flops en el estado "0", no hay ninguna contribución al peso numérico del contador, el cual se puede decir que se encuentra en el estado cero.

Cuando el contador ha salido del estado "0000" pasa al estado "1000", y como el conteo debe ser decimal ascendente, esto significa que tenemos que darle al primer flip-flop un peso numérico de 1, lo cual es puesto en la columna "Conclusión".

Cuando el contador pasa del estado "1000" al estado "0100", si hemos de mantener la cuenta decimal ascendente esto significa que tenemos que darle al segundo flip-flop un peso numérico de 2. Cada vez que se "encienda" el segundo flip-flop con un "1" contribuirá un peso numérico de 2, lo cual es puesto en la columna "Conclusión".

Cuando el contador pasa del estado "0100" al estado "1100", el conteo decimal acumulativo es 3, porque cada uno de los dos primeros flip-flops contribuye con un peso numérico de 1 y de 2, respectivamente, o sea que 1+2=3.

Cuando el contador pasa del estado "1100" al estado "0110", puesto que el número decimal que sigue debe ser 4, y el segundo flip-flop ya está contribuyendo con un peso numérico de 2, esto significa que el tercer flip-flop necesariamente debe tener también un peso numérico de 2.

Procediendo de la misma manera, concluímos que el cuarto flip-flop debe tener un peso numérico de 4.

Entonces, el peso del contador es 1-2-2'-4.

Estudiando el contador, se nota que está compuesto por dos secciones. La primera es básicamente un contador módulo-2 (o contador binario) realizada por el primer flip-flop. La segunda que le sigue es básicamente un contador módulo-5 (o contador quinario) realizada por los siguientes tres flip-flops. Por lo tanto, este contador recibe el nombre de contador bi-quinario y su importancia radica en que es un contador base 10 o base decimal.

PROBLEMA: El Bucket Brigade. Analizar el siguiente circuito construyendo una tabla de secuencias para el mismo. Supóngase que al empezar el circuito está en el estado Q1Q2Q3Q4=1000. (Obsérvese que, en contra de lo acostumbrado en los circuitos lógicos anteriores, estamos usando la salida complementaria del primer flip-flop y no su salida normal Q) ¿Cuál es el módulo de este contador?

Siendo la condición inicial Q1Q2Q3Q4=01000, los estados sucesivos después de cada transición serán los siguientes:

Primera transición: El estado es Q1Q2Q3Q4=0100.

Segunda transición: El estado es Q1Q2Q3Q4=0010.

Tercera transición: El estado es Q1Q2Q3Q4=0001.

Cuarta transición: El estado es Q1Q2Q3Q4=1000.

La tabla de secuencias que resume el comportamiento del circuito es la siguiente:

Puesto que el contador recorre cuatro estados diferentes para así regresar a la condición inicial, es un contador módulo-4. Todos los elementos de esta configuración (con la excepción del primero, el cual está "invertido" en sus conexiones con respecto a los demás) están conectados de igual manera. Esto sugiere que se puede construír un contador módulo-N cualesquiera utilizando un número N de flip-flops para construírlo bajo esta configuración, aunque la salida del circuito no será simétrica. Nótese que el Bucket Brigade se puede usar como un contador de anillo.

El nombre "Bucket Brigade" deviene del significado de la palabra inglesa "bucket" que significa "cubeta", o sea, "la brigada de la cubeta", en referencia a una cubeta de agua que se iban pasando los miembros de la brigada del uno al otro haciéndola de bomberos para tratar de apagar un incendio, excepto que aquí la "cubeta" es un "1" lógico.

PROBLEMA: Diseñar, empleando el método que sea, un contador que produzca la siguiente secuencia:

Puesto que cada uno de los estados mostrado por la tabla de secuencias es diferente, no habiendo un estado igual a otro, este problema se presta a su resolución retroalimentando la salida de una memoria ROM a su entrada, de modo tal que cada estado contenido en cualquier domicilio sea a su vez el domicilio del ROM que contenga el siguiente domicilio que la vez será el siguiente estado del contador.

De la tabla de secuencias podemos primeramente construír la tabla requerida de la memoria ROM:

Esta es la especificación del ROM. Podemos acomodar los valores en la forma acostumbrada, con los domicilios en orden binario ascendente:

Con esto tenemos todo lo necesario para "quemar" un ROM y construír, agregando una compuerta de flip-flops D, el circuito secuencial deseado.

PROBLEMA: Diseñar, empleando el método que sea, un contador que produzca la siguiente secuencia:

Aunque a primera vista pueda resultar tentador recurrir a la técnica de emplear un ROM en el cual cada estado sea el domicilio del ROM que contenga el siguiente domicilio que la vez sea el siguiente estado del contador, una inspección detallada de la tabla de secuencias revela que esto no será posible, ya que del segundo renglón que además de ser el estado "000" correspondería al domicilio "000" en donde tenemos el siguiente estado "010" (que a su vez sería el domicilio del siguiente estado) se contraviene con el séptimo renglón en el cual se le pide al domicilio "000" apuntar a otro estado, hacia el estado "001". En pocas palabras, se le pediría al mismo domicilio del ROM apuntar hacia dos domicilios diferentes, y esto es algo que el ROM no puede hacer. Esto nos lleva a considerar utilizar un contador binario ascendente conectando sus salidas hacia un circuito lógico combinatorio o hacia un ROM. Lo haremos primero tratando de conectar las salidas del contador binario hacia un circuito combinatorio. Con esto, estamos requiriendo hacer la siguiente conversión de una secuencia binaria a una secuencia prefijada de antemano:

Esto es relativamente fácil de lograr mediante una red de lógica combinatoria que transforme los estados de la secuencia binaria en los estados de la secuencia dada. Cada valor requerido para formar la secuencia deseada se puede obtener a través de los minterms producidos por los estados de la secuencia binaria como se muestra a continuación (obsérvese que a estas alturas estamos hablando ya no de una tabla de secuencias sino en realidad de tres Tablas de Verdad diferentes):

Para Q'1 tenemos, usando minterms:

Q'1 = Q1Q2Q3 + Q1Q2Q3

Q'1 = Q1Q2(Q3 + Q3)

Q'1 = Q1Q2

Q'1 = (Q1 + Q2)'

Q'1 = Q1Q2(Q3 + Q3)

Q'1 = Q1Q2

Q'1 = (Q1 + Q2)'

Esta es una función NOR (obsérvese el uso de la notación alterna al final para indicar el inverso).

Q'2 = Q1Q2Q3 + Q1Q2Q3 + Q1Q2Q3 + Q1Q2Q3

Q'2 = (Q1 + Q1)Q2Q3 + (Q1 + Q1)Q2Q3

Q'2 = Q2Q3 + Q2Q3

Q'2 = (Q1 + Q1)Q2Q3 + (Q1 + Q1)Q2Q3

Q'2 = Q2Q3 + Q2Q3

Esta es una función OR-EXCLUSIVO.

Q'3 = Q1Q2Q3 + Q1Q2Q3

Q'3 = Q1Q3(Q2 + Q2)

Q'3 = Q1Q3

Q'3 = Q1Q3(Q2 + Q2)

Q'3 = Q1Q3

Esta es una función AND.

El diagrama del contador se muestra a continuación:

PROBLEMA: ¿Cuántos estados denegados tiene un Bucket Brigade de 4 bits? ¿De n bits? ¿De 5 bits? ¿De 6 bits?

Comparamos primero la secuencia natural del Bucket Brigade de 4 bits:

con todos sus estados posibles:

Podemos ver que hay doce posibles estados denegados. Conociendo la forma en la cual trabaja el Bucket Brigade, observamos que no hay ninguna manera en la cual se pueda "sacar" por sí solo de cualquiera de los doce posibles estados denegados. Concluímos pues que un Bucket Brigade de 4 bits tendrá doce estados denegados.

En general, un Bucket Brigade de n bits tendrá una secuencia natural de n estados, esto de un total de 2n estados posibles. Tendrá por lo tanto 2n-n estados denegados.

Sobre esta fórmula general, un Bucket Brigade de 5 bits tendrá 25-5 = 27 estados denegados.

Del mismo modo, un Bucket Brigade de 6 bits tendrá 26-6 = 58 estados denegados.

PROBLEMA: Analizar el siguiente contador.

Suponiendo que el contador está inicialmente en la condición Q1Q2Q3Q4=0000 al empezar, observamos al trabajar sobre el diagrama en cada etapa lo siguiente:

Primera transición: El estado es Q1Q2Q3Q4=1000.

Segunda transición: El estado es Q1Q2Q3Q4=0100.

Tercera transición: El estado es Q1Q2Q3Q4=1100.

Cuarta transición: El estado es Q1Q2Q3Q4=0010.

Quinta transición: El estado es Q1Q2Q3Q4=1010.

Sexta transición: El estado es Q1Q2Q3Q4=0110.

Séptima transición: El estado es Q1Q2Q3Q4=1110.

Octava transición: El estado es Q1Q2Q3Q4=0001.

Novena transición: El estado es Q1Q2Q3Q4=1001.

Décima transición: El estado es Q1Q2Q3Q4=0000.

La secuencia nos revela inmediatamente que este es un contador binario decimal con peso 1-2-4-8; esto es, un contador binario BCD.

Este tipo de contador desempeña un papel vital en el uso práctico de los circuitos lógicos, ya que nos permite contar en el sistema decimal usando una secuencia binaria. Si a la terminal "reloj" la designamos "contar" y a la terminal de "salida" la designamos "llevar", funcionalmente el circuito presentará el siguiente aspecto:

Si conectamos las salidas del contador binario BCD a un indicador luminoso de siete segmentos mediante un decodificador, tendremos una unidad de conteo digital decimal:

Esta unidad es el bloque fundamental de los contadores electrónicos usados en las carátulas digitales de los televisores, de los hornos de microondas, de los relojes despertadores, de los sintonizadores de radio, en fin, las aplicaciones son inagotables.

Para construír un contador de 3 dígitos decimales, por ejemplo, basta con conectar tres unidades como la de arriba en serie. La terminal "llevar" de la primera unidad se conecta a la terminal "contar" de la segunda unidad y la terminal "llevar" de la segunda unidad se conecta a la terminal "contar" de la tercera unidad. La terminal "llevar" de la tercera unidad se puede utilizar para indicar un sobreflujo S. Tomando en cuenta que un conteo ascendente procede de derecha a izquierda, el contador aparecerá de la siguiente manera:

La terminal de sobreflujo se puede utilizar para "limpiar" el contador además de indicar la presencia del mismo sobreflujo.

Un diseño de este tipo no sería muy útil en la práctica porque este contador es asíncrono, los flip-flops J-K que lo componen no son activados simultáneamente por la misma señal de "reloj", y por lo tanto no es el circuito más rápido posible. Se puede modificar este diseño para convertirlo en un contador binario BCD síncrono. Y se puede refinar aún más para convertirlo en un contador que no sólo sea capaz de contar "hacia arriba" (up counter) sino también hacia abajo (down counter). Como puede suponerse, el diseño final de algo como lo último resultará algo elaborado. Afortunadamente, no es necesario esforzarse en un proyecto de esta naturaleza, ya que es posible adquirir en el mercado a un precio sumamente bajo un circuito integrado que tenga todas estas virtudes, como el 4510:

en el cual las salidas BCD Q1, Q2, Q4 y Q8 aparecen en las terminales 6, 11, 14 y 2, respectivamente, con la terminal de "contar" (reloj) en la terminal 15 y la terminal de "llevar" (Carry Out) en la terminal 7. El conteo será ascendente si la terminal 10 (Up/Down) tiene puesto un "cero" y será descendente si tiene puesto un "1". El contador se puede "cargar" con un número predeterminado a través de las terminales 4, 12, 13 y 3, identificadas como L1, L2, L4 y L8, para lo cual hay que poner un "1" momentáneamente en la terminal 1 (Load); y también puede ser puesto en "ceros" poniendo un "1" en la terminal 1 (RST).

PROBLEMA: Derivar para un flip-flop J-K las ecuaciones Boleanas de sus entradas J y K en función de Qn (el estado del flip-flop J-K previo a una transición) y de Qn+1 (el estado del flip-flop J-K después de que ha ocurrido una transición al siguiente estado).

La postulación de este problema puede al principio parecer desconcertante, dado que hasta este momento hemos estado acostumbrados a pensar en J y K como entradas que sirven para condicionar al flip-flop J-K hacia su siguiente estado. Sin embargo, en principio, no hay nada que nos detenga para llevar a cabo este procedimiento. Una forma de verlo es como el tratar de determinar los valores que deben tener J y K para producir las transiciones deseadas de un estado a otro.

Más importante aún es la sutileza de lo que está por llevarse a cabo, ya que vamos a transformar una tabla de secuencias en una Tabla de Verdad. Aquí veremos que el paso que separa una tabla de secuencias para un circuito secuencial de una Tabla de Verdad es en realidad un paso muy endeble.

Empezamos pues usando una tabla de secuencias que describa en forma completa las propiedades del flip-flop J-K:

Con un simple reacomodo de las columnas podemos ver a J y K como "salidas" Boleanas en función de las "entradas" Qn y Qn+1:

Obtenemos primero J en función de Qn y Qn+1 de por medio de minterms:

J = QnQn+1 + QnQn+1 + QnQn+1 + QnQn+1

J = Qn(Qn+1 + Qn+1) + QnQn+1

J = QnQn+1 + Qn

J = Qn(Qn+1 + Qn+1) + QnQn+1

J = QnQn+1 + Qn

Obtenemos ahora K usando el mismo procedimiento:

K = QnQn+1 + QnQn+1 + QnQn+1 + QnQn+1

K = QnQn+1 + Qn(Qn+1 + Qn+1)

K = Qn + QnQn+1

K = QnQn+1 + Qn(Qn+1 + Qn+1)

K = Qn + QnQn+1

PROBLEMA: Diseñar, usando flip-flops J-K, un contador síncrono cuya secuencia natural de estados sea la siguiente:

Una inspección preliminar de este problema nos indica que tratar de llevar a cabo su solución por intuición únicamente puede ser bastante difícil. Optamos entonces por recurrir a un método más formal desprovisto de "trucos".

Para empezar, podemos preparar unas tablas de secuencias en las cuales relacionamos los estados del contador previos a una transición con los estados del contador después de que ha ocurrido una transición:

Usando minterms, encontramos que para este contador:

Q1n+1 = Q1nQ2n + Q1nQ2n

Q1n+1 = Q1n(Q2n + Q2n)

Q1n+1 = Q1n

Q2n+1 = Q1nQ2n + Q1nQ2n

Q1n+1 = Q1n(Q2n + Q2n)

Q1n+1 = Q1n

Q2n+1 = Q1nQ2n + Q1nQ2n

Usando los resultados del problema anterior, podemos obtener las entradas requeridas por el primer flip-flop J-K del contador:

J1 = Q1nQ1n+1 + Q1n

J1 = Q1n(Q1n) + Q1n

J1 = Q1n

J1 = Q1n(Q1n) + Q1n

J1 = Q1n

K1 = Q1n + Q1nQ1n+1

K1 = Q1n + Q1nQ1n

K1 = Q1n

K1 = Q1n + Q1nQ1n

K1 = Q1n

Obtenemos ahora las entradas requeridas por el segundo flip-flop J-K del contador:

J2 = Q2nQ2n+1 + Q2n

J2 = Q2n(Q1nQ2n +Q1nQ2n) + Q2n

J2 = Q2nQ1nQ2n + Q1nQ2n + Q2n

J2 = Q1nQ2n + Q2n

J2 = Q2n(Q1nQ2n +Q1nQ2n) + Q2n

J2 = Q2nQ1nQ2n + Q1nQ2n + Q2n

J2 = Q1nQ2n + Q2n

Usando el mapa de Karnaugh, es posible simplificar aún más esta expresión:

J2 = Q1n + Q2n

Ahora procedemos a la obtención de K2:

K2 = Q2n + Q2nQ2n+1

K2 = Q2n + Q2n(Q1n + Q2n)(Q1n + Q2n)

K2 = Q2n + Q2n(Q1nQ1n + Q1nQ2n + Q1nQ2n + Q2nQ2n)

K2 = Q2n + Q2n(Q1nQ2n + Q1nQ2n)

K2 = Q2n + Q1nQ2n

K2 = Q2n + Q2n(Q1n + Q2n)(Q1n + Q2n)

K2 = Q2n + Q2n(Q1nQ1n + Q1nQ2n + Q1nQ2n + Q2nQ2n)

K2 = Q2n + Q2n(Q1nQ2n + Q1nQ2n)

K2 = Q2n + Q1nQ2n

Esta expresión también se puede simplificar usando el mapa de Karnaugh:

K2 = Q1n + Q2n

Tomando en cuenta los resultados obtenidos, el diseño del contador toma el siguiente aspecto:

Observamos que en el primer flip-flop J-K, las salidas complementarias están conectadas de modo invertido a las entradas J y K. Esto ocasiona que el primer flip-flop J-K actúe como un simple divisor binario o flip-flop T. Pero podemos obtener la misma acción con J=0 y K=0, lo cual simplifica el diseño. En general, cuando las salidas están conectadas en forma inversa a las entradas, estas entradas se pueden reemplazar con la condición J=0 y K=0, aprovechando la enorme versatilidad del flip-flop J-K para ello. El segundo flip-flop se presta también a esta simplificación. El diseño toma entonces el siguiente aspecto:

La siguiente simplificación es obvia. El diseño toma por fin su aspecto final:

PROBLEMA: Derivar para un flip-flop D la ecuación de su entrada D en función de Qn (el estado del flip-flop D previo a una transición) y de Qn+1 (el estado del flip-flop D después de que ha ocurrido una transición al siguiente estado).